| Diseñador | Intel |

|---|---|

| Bits | 32/64 bits |

| Introducido | 1989 |

| Diseño | RISC , VLIW |

| Tipo | Registrarse-Registrarse |

| Codificación | Reparado |

| Derivación | Comparar y bifurcar |

| Endianidad | Bi |

| Tamaño de página | 4 KiB |

| Extensiones | Unidad gráfica de 64 bits |

| Registros | |

| Propósito general | 32 32 bits |

| Punto flotante | 32 32 bits (16 64 bits) |

El Intel i860 (también conocido como 80860 ) fue un diseño de microprocesador RISC introducido por Intel en 1989. Fue uno de los primeros intentos de Intel en una arquitectura de conjunto de instrucciones de alta gama completamente nueva desde el fallido Intel iAPX 432 de la década de 1980. Fue lanzado con considerable fanfarria, oscureciendo ligeramente el anterior Intel i960 , que tuvo éxito en algunos nichos de sistemas integrados y que muchos consideraron un mejor diseño. El i860 nunca alcanzó el éxito comercial y el proyecto se terminó a mediados de la década de 1990.

Implementaciones [ editar ]

Microprocesador Intel i860 XR (edición de 33 MHz) | |

| Información general | |

|---|---|

| Lanzado | 1989 |

| Interrumpido | mediados de la década de 1990 |

| Fabricante (s) común (es) |

|

| Rendimiento | |

| Max. Frecuencia de reloj de la CPU | 25 MHz a 40 MHz |

| Cache | |

| Caché L1 | 4 KB (I) + 8 KB (D) |

| Arquitectura y clasificación | |

| Conjunto de instrucciones | Intel i860 |

| Especificaciones físicas | |

| Núcleos |

|

| Historia | |

| Sucesor | i860 XP |

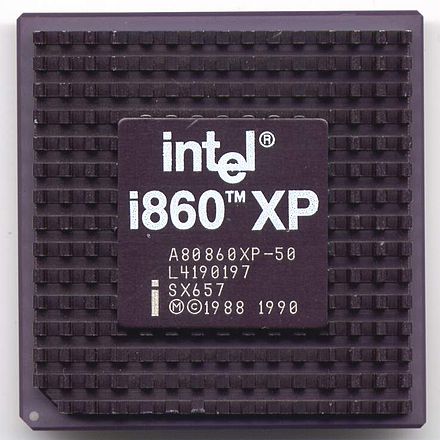

La primera implementación de la arquitectura i860 fue el microprocesador i860 XR (nombre en código N10 ), que funcionaba a 25, 33 o 40 MHz. El microprocesador i860 XP de segunda generación (nombre en código N11 ) agregó páginas de 4 Mbyte, cachés en chip más grandes, soporte de caché de segundo nivel, buses más rápidos y soporte de hardware para rastreo de bus, para consistencia de caché en sistemas multiprocesador . Una reducción de proceso para el XP (de 1 micrómetro a 0,8 CHMOS V) lo elevó a 40 y 50 MHz. [1] Ambos microprocesadores admitían el mismo conjunto de instrucciones para programas de aplicación.

Características técnicas [ editar ]

El i860 combinó una serie de características que eran únicas en ese momento, sobre todo su arquitectura de palabra de instrucción muy larga (VLIW) y su potente soporte para operaciones de punto flotante de alta velocidad. [2] El diseño montó un "Núcleo" ALU de 32 bits junto con una FPU de 64 bits que se construyó en tres partes: un sumador, un multiplicador y un procesador de gráficos. El sistema tenía tuberías separadas para la ALU, sumador de punto flotante y multiplicador, y podía entregar hasta tres operaciones por reloj. (Es decir, dos instrucciones: una instrucción de número entero y una instrucción de multiplicación y acumulación de coma flotante por reloj).

Todos los buses tenían al menos 64 bits de ancho. El bus de memoria interna al caché, por ejemplo, tenía 128 bits de ancho. Ambas unidades tenían treinta y dos registros de 32 bits, pero la FPU usó su conjunto como dieciséis registros de 64 bits. Las instrucciones para la ALU se obtuvieron de dos en dos para usar el bus externo completo. Intel se refirió al diseño como el "microprocesador i860 de 64 bits". [3]

Las instrucciones de Intel i860 actuaron sobre tamaños de datos de 8 bits a 128 bits. [4]

La unidad gráfica era única para la época. Básicamente, era una unidad entera de 64 bits que usaba los registros FPU como ocho registros de 128 bits. Admitía una serie de comandos para instrucciones similares a SIMD además de matemáticas básicas de enteros de 64 bits. La experiencia con el i860 influyó en la funcionalidad MMX que luego se agregó a los procesadores Pentium de Intel.

Una característica inusual del i860 era que las tuberías hacia las unidades funcionales eran accesibles desde el programa ( VLIW ), lo que requería que los compiladores ordenaran las instrucciones cuidadosamente en el código objeto.para mantener las tuberías llenas. En las arquitecturas tradicionales, estas tareas se manejaban en tiempo de ejecución por un programador en la propia CPU, pero la complejidad de estos sistemas limitaba su aplicación en los primeros diseños de RISC. El i860 fue un intento de evitar esto por completo moviendo este deber fuera del chip al compilador. Esto permitió que el i860 dedicara más espacio a las unidades funcionales, mejorando el rendimiento. Como resultado de su arquitectura, el i860 podía ejecutar ciertos gráficos y algoritmos de punto flotante con una velocidad excepcionalmente alta, pero su rendimiento en aplicaciones de propósito general se resintió y era difícil programar de manera eficiente (ver más abajo).

Rendimiento [ editar ]

Sobre el papel, el rendimiento fue impresionante para una solución de un solo chip; sin embargo, el desempeño en el mundo real fue todo lo contrario. Un problema, quizás no reconocido en ese momento, fue que las rutas del código en tiempo de ejecución son difíciles de predecir, lo que significa que se vuelve extremadamente difícil ordenar las instrucciones correctamente en el momento de la compilación . Por ejemplo, una instrucción para sumar dos números tomará mucho más tiempo si los datos no están en la caché, pero el programador no tiene forma de saber si lo están o no. Si se realiza una suposición incorrecta, toda la tubería se detendrá, esperando los datos. Todo el diseño del i860 se basó en que el compilador manejara eficientemente esta tarea, lo que resultó casi imposible en la práctica. Si bien teóricamente es capaz de alcanzar un máximo de aproximadamente 60-80 MFLOPS tanto para precisión simple como paradoble precisión para las versiones de XP, [5] el código ensamblador escrito manualmente logró obtener solo alrededor de 40 MFLOPS, y la mayoría de los compiladores tuvieron dificultades para obtener incluso 10 MFLOP. [6] La arquitectura Itanium posterior , también un diseño VLIW, sufrió nuevamente el problema de los compiladores incapaces de entregar un código suficientemente optimizado.

Otro problema grave fue la falta de una solución para manejar rápidamente el cambio de contexto . El i860 tenía varias tuberías (para las partes de ALU y FPU) y una interrupción podría derramarlas y requerir que todas se recarguen. Esto tomó 62 ciclos en el mejor de los casos y casi 2000 ciclos en el peor. Este último es 1/20000 de segundo a 40 MHz (50 microsegundos), una eternidad para una CPU. Esto eliminó en gran medida el i860 como CPU de propósito general.

Fallecimiento [ editar ]

A medida que los compiladores mejoraron, el rendimiento general del i860 hizo lo mismo, pero para entonces la mayoría de los otros diseños RISC ya habían superado al i860 en rendimiento.

A fines de la década de 1990, Intel reemplazó toda su línea RISC con diseños basados en ARM , conocidos como XScale . Confusamente, el número 860 se ha reutilizado desde entonces para un conjunto de chips de control de placa base para sistemas Intel Xeon ( Pentium de gama alta ) y un modelo del Core i7.

Andy Grove sugirió que la falla del i860 en el mercado se debió a que Intel se estiró demasiado:

Ahora teníamos dos chips muy potentes que estábamos introduciendo casi al mismo tiempo: el 486, basado en gran parte en la tecnología CISC y compatible con todo el software de PC, y el i860, basado en la tecnología RISC, que era muy rápido pero compatible con ninguna cosa. No sabíamos qué hacer. Así que presentamos ambos, pensando que dejaríamos que el mercado decidiera. ... nuestro equívoco hizo que nuestros clientes se preguntaran qué representaba realmente Intel, ¿el 486 o el i860?

- Andy Grove , [7]

Aplicaciones [ editar ]

Al principio, el i860 solo se usó en una pequeña cantidad de supercomputadoras como Intel iPSC / 860 . Posteriormente, Intel comercializó el i860 como un microprocesador de estación de trabajo durante un tiempo, donde compitió con microprocesadores basados en las arquitecturas MIPS y SPARC , entre otros. Las estaciones de trabajo Unix Oki Electric OKI Station 7300/30 [8] y Stardent Vistra 800 [9] se basaron en un i860 XR de 40 MHz con UNIX System V / i860. [10] The Hauppauge 4860 [11] y Olivetti CP486 [12]presentó un Intel 80486 y un i860 en la misma placa base. Microsoft desarrolló inicialmente lo que se convertiría en Windows NT en estaciones de trabajo basadas en i860XR diseñadas internamente (con nombre en código Dazzle ), y solo transfirió NT a MIPS ( Microsoft Jazz ), Intel 80386 y otros procesadores más tarde. Algunos afirman que la designación NT era una referencia al nombre en clave "N-Ten" del i860XR. [13]

El i860 tuvo algún uso en el mundo de las estaciones de trabajo como acelerador de gráficos. Se usó, por ejemplo, en NeXTdimension , donde ejecutó una versión reducida del kernel de Mach ejecutando una pila PostScript completa . Sin embargo, la parte PostScript del proyecto nunca se terminó, por lo que terminó simplemente moviendo píxeles de color. En esta función, el diseño del i860 funcionó considerablemente mejor, ya que el programa principal podía cargarse en la caché y hacerse completamente "predecible", lo que permitía a los compiladores realizar el pedido correctamente. Truevision produjo una placa aceleradora basada en i860 diseñada para usar con sus tarjetas de framebuffer Targa y Vista. Pixarprodujo una versión personalizada de RenderMan para ejecutar en la tarjeta que se ejecutó aproximadamente cuatro veces más rápido que el host 386. Otro ejemplo fue el RealityEngine de SGI , que utilizó varios procesadores i860XP en su motor de geometría. Este tipo de uso también desapareció lentamente, a medida que las CPU de uso general comenzaron a igualar el rendimiento del i860, y cuando Intel se centró en los procesadores Pentium para la informática de uso general.

Mercury Computer Systems utilizó el i860 en su multicomputadora . De 2 a 360 nodos de cómputo residirían en una red de árbol gordo con conmutación de circuitos , y cada nodo tendría una memoria local que podría ser mapeada por cualquier otro nodo. Cada nodo de este sistema heterogéneo podría ser un i860, un PowerPC o un grupo de tres DSP SHARC . Se obtuvo un buen rendimiento del i860 al proporcionar a los clientes una biblioteca de funciones de procesamiento de señales escritas en lenguaje ensamblador. El hardware empaquetaba hasta 360 nodos de cómputo en 9U de espacio de rack , lo que lo hace adecuado para aplicaciones móviles como el procesamiento de radares aéreos.

A principios de la década de 1990, Stratus Technologies construyó servidores basados en i860, la serie XA / R, que ejecutaban su sistema operativo VOS patentado . [14]

También en la década de 1990, Alliant Computer Systems construyó sus servidores FX / 800 y FX / 2800 basados en i860, reemplazando las series FX / 80 y FX / 8 que se habían basado en el Motorola 68000 ISA. Tanto los sistemas informáticos Alliant como Mercury se utilizaron mucho en la NASA / JPL para las misiones SIR-C .

El ejército de los EE. UU. Utilizó el i860 para numerosas aplicaciones de procesamiento de señales digitales y aeroespaciales como coprocesador, donde se utilizó hasta finales de la década de 1990. [15]

| Wikimedia Commons tiene medios relacionados con Intel i860 . |

Referencias [ editar ]

- ^ El i860 XP - Segunda generación del i860.

- ^ Kohn, Les; Margulis, N. (1989). "Presentamos el microprocesador Intel i860 de 64 bits". Sociedad de Informática IEEE: 15–30. Cite journal requires

|journal=(help) - ^ Grimes, Jack; Kohn, L .; Bharadhwaj, R. (1989). "El procesador Intel i860 de 64 bits: una CPU de uso general con capacidades de gráficos 3D". Sociedad de Informática IEEE: 85–94. Cite journal requires

|journal=(help) - ^ "La colección de chips - microprocesador i860 - Smithsonian Institution" .

- ^ Oleg Yu. Repin, Alexei S. Pylkin (2000). "Intel i860: microprocesador de 64 bits" . sscc.ru, ICMMG. Archivado desde el original el 23 de junio de 2009 . Consultado el 27 de septiembre de 2013 .

- ^ DH Bailey, E. Barszcz, RA Fatoohi, HD Simon, S. Weeratunga (1990). Resultados de rendimiento del prototipo Intel Touchstone Gamma (PDF) (Informe). Centro de Investigación Ames de la NASA. CS1 maint: uses authors parameter (link)

- ^ La CPU 486 de Intel cumple 15 años | Geek.com Archivado el 25 de mayo de 2008 en la Wayback Machine.

- ^ "Oki Electric OKI Station 7300/30-Computer Museum" .

- ^ "Intel i860 - de aquí para allá" . 2010.

- ^ "Computadora KUBOTA / Stardent AVSstation Titan Vistra 800" . Archivado desde el original el 14 de mayo de 2014 . Consultado el 14 de mayo de 2014 .

- ^ "GeekDot - Hauppauge 4860" .

- ^ "GeekDot - Olivetti CP486" .

- ↑ Thurrott, Paul (24 de enero de 2003). "Windows Server 2003: el camino hacia el oro" . Gana super sitio . Archivado desde el original el 20 de julio de 2011 . Consultado el 2 de septiembre de 2013 .

- ^ "Historia de la máquina Stratus" .

- ^ http://www.militaryaerospace.com/articles/print/volume-8/issue-5/features/technology-focus/cots-board-vendors-make-their-dsp-choices.html

- Margulis, Neal (1990). Arquitectura del microprocesador i860 . Osborne / McGraw-Hill. ISBN 978-0-07-881645-1.

Enlaces externos [ editar ]

- Muchas tarjetas de expansión i860

- Imágenes y descripción del i860 .

- Rhodehamel, Michael W. " La interfaz de bus y las unidades de localización del microprocesador i860 (tm) ". En Proc. Conferencia Internacional IEEE sobre Diseño de Computadoras, p. 380–384, 1989.