La optimización lógica , una parte de la síntesis lógica en electrónica , es el proceso de encontrar una representación equivalente del circuito lógico especificado bajo una o más restricciones especificadas. Generalmente, el circuito está limitado a un área de chip mínima que cumple un retardo preespecificado.

Introducción

Con el advenimiento de la síntesis lógica , uno de los mayores desafíos que enfrentó la industria de la automatización del diseño electrónico (EDA) fue encontrar la mejor representación de la lista de conexiones de la descripción de diseño dada. Si bien la optimización lógica de dos niveles había existido durante mucho tiempo en la forma del algoritmo Quine-McCluskey , seguido más tarde por el minimizador lógico heurístico Espresso , las densidades de chips que mejoran rápidamente y la amplia adopción de HDL para la descripción de circuitos, formalizaron el dominio de optimización lógica como existe hoy.

Hoy, la optimización lógica se divide en varias categorías:

Basado en la representación del circuito

- Optimización lógica de dos niveles

- Optimización lógica multinivel

Basado en las características del circuito

- Optimización de lógica secuencial

- Optimización de lógica combinacional

Según el tipo de ejecución

- Métodos de optimización gráfica

- Métodos de optimización tabular

- Métodos de optimización algebraica

Mientras que una representación de un circuito de dos niveles de los circuitos se refiere estrictamente a la vista aplanada del circuito en términos de procedimientos normalizados de trabajo ( suma de los productos ) - que es más aplicable a una PLA implementación del diseño [ aclaración necesaria ] - un multi-nivel representación es una vista más genérico del circuito en términos de SOPs arbitrariamente conectados, POS ( producto de sumas ), forma factorizada etc. Logic algoritmos de optimización generalmente funciona bien en las estructurales (SOPs, forma factorizada) o funcionales ( BDDs , añade ) representación del circuito. [ aclaración necesaria ]

Representaciones de dos niveles frente a representaciones de varios niveles

Si tenemos dos funciones F 1 y F 2 :

La representación de 2 niveles anterior toma seis términos de producto y 24 transistores en CMOS Rep. [ ¿Por qué? ]

Una representación funcionalmente equivalente en multinivel puede ser:

- P = B + C .

- F 1 = AP + AD .

- F 2 = A'P + A'E .

Si bien el número de niveles aquí es 3, el número total de términos de producto y literales se reduce [ cuantifica ] debido a que se comparte el término B + C.

De manera similar, distinguimos entre circuitos secuenciales y combinacionales , cuyo comportamiento puede describirse en términos de tablas / diagramas de estados de máquinas de estados finitos o mediante funciones y relaciones booleanas, respectivamente. [ aclaración necesaria ]

Minimización de circuitos en álgebra booleana

En álgebra booleana , la minimización de circuitos es el problema de obtener el circuito lógico más pequeño (fórmula booleana) que represente una función booleana dada o una tabla de verdad . Para el caso en el que la función booleana es especificada por un circuito (es decir, queremos encontrar un circuito equivalente de tamaño mínimo posible), el problema de minimización del circuito ilimitado se conjeturó durante mucho tiempo como-completo , resultado finalmente probado en 2008, [1] pero existen heurísticas efectivas como los mapas de Karnaugh y el algoritmo de Quine-McCluskey que facilitan el proceso.

Los métodos de minimización de funciones booleanas incluyen:

- Método Blake - Poretsky

- Método Nelson [2] [3] [4] [5] [6]

- Algoritmo de Quine-McCluskey

- método de transformaciones algebraicas

- El método de Petrick

- Método Roth [7] [8] [9]

- Método Kudielka [10] [11] [12]

- Método de Wells [13]

- Método binario de Scheinman [14] [15]

- un método para minimizar funciones en las bases YES-NO y OR-NOT (base de Schaeffer y Pierce)

- método de coeficientes indeterminados

- método hipercubo

- método de descomposición funcional

- Minimizador de lógica heurística de espresso

Propósito

El problema de tener un circuito complicado (es decir, uno con muchos elementos, como puertas lógicas ) es que cada elemento ocupa espacio físico en su implementación y cuesta tiempo y dinero producirlo en sí mismo. La minimización de circuitos puede ser una forma de optimización lógica utilizada para reducir el área de lógica compleja en circuitos integrados .

Ejemplo

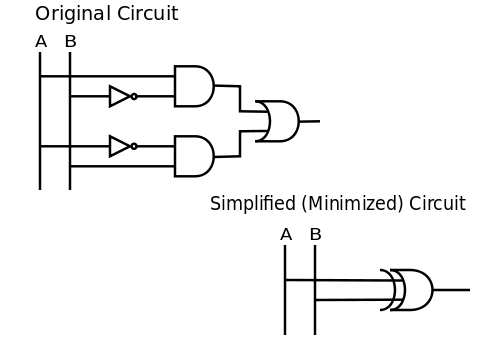

Si bien hay muchas formas de minimizar un circuito, este es un ejemplo que minimiza (o simplifica) una función booleana. Tenga en cuenta que la función booleana llevada a cabo por el circuito está directamente relacionada con la expresión algebraica a partir de la cual se implementa la función. [16] Considere el circuito utilizado para representar. Es evidente que en este enunciado se utilizan dos negaciones, dos conjunciones y una disyunción. Esto significa que para construir el circuito se necesitarían dos inversores , dos puertas AND y una puerta OR .

Podemos simplificar (minimizar) el circuito aplicando identidades lógicas o utilizando la intuición. Dado que el ejemplo establece que A es verdadero cuando B es falso o al revés, podemos concluir que esto simplemente significa. En términos de puertas lógicas, la desigualdad simplemente significa una puerta XOR (exclusiva o). Por lo tanto,. Entonces los dos circuitos que se muestran a continuación son equivalentes:

Además, puede verificar la exactitud del resultado utilizando una tabla de verdad .

Métodos de minimización de lógica gráfica

Los métodos de minimización gráfica para la lógica de dos niveles incluyen:

- Diagrama de Euler (también conocido como círculo euleriano ) (1768) de Leonhard P. Euler (1707-1783)

- Diagrama de Venn (1880) de John Venn (1834-1923) [17] [18]

- Diagrama de Marquand (1881) de Allan Marquand (1853-1924) [19] [20]

- Gráfico de minimización de Harvard (también conocido como gráfico de Harvard ) (1951) de Howard H. Aiken (1900-1973) y Martha L. Whitehouse [21] [22] [23] [24] [15] del Laboratorio de Computación de Harvard

- Gráfico de descomposición (1952) de Robert L. Ashenhurst (1929-2009) y Theodore Singer (1916-1991) [25] [26] [27] [24] del Laboratorio de Computación de Harvard

- Gráfico de Veitch (1952) de Edward W. Veitch (1924-2013) [28] [20]

- Mapa de Karnaugh (1953) de Maurice Karnaugh (1924–) [22] [24]

- Huesos de contacto , rejillas de contacto (1955) y el mapa triádico de Antonín Svoboda (1907-1980) [29] [30] [31] [32] [33] [34] [35] [36] [37] [38 ] [39] [40] [41] [42]

- Método gráfico (1957) de Vadim Nikolaevich Roginskij [43] [ Вадим Николаевич Рогинский ] (1913-1983) [44] [45] [46] [36]

- Diagrama de Händler (también conocido como gráfico circular de Händler , Händler'scher Kreisgraph , Kreisgraph nach Händler , Händler-Kreisgraph , Händler-Diagramm , Minimisierungsgraph , M n graph ) (1958) de Wolfgang Händler (1920-1998) [47] [48] [49 ] [41] [50] [51] [52] [53] [54] [55] [56] [57] [58]

- Mapa de Mahoney también conocido como mapa M o números de designación (1963) de Matthew V. Mahoney [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71]

- Método gráfico (1965) de Herbert F. Kortum (1907-1979) [72] [73] [74] [75] [76] [77] [78] [79] [80] [81]

- Mapa de Karnaugh reducida (RKM) [82] [83] [84] técnicas alias de variables poco frecuentes (1969) por GW Schultz, [85] [86] [87] asignar a entrar en las variables (MEV, 1969) por Thomas E. Osborne [ 86] y Christopher R. Clare, [88] [89] [90] [91] [92] [93] [94] [95] [83] [84] Mapa de Karnaugh con variables de nombre de letra (1972) por J Robert Burgoon [82] [96] y Larry L. Dornhoff (1942-2017), [90] mapa de Karnaugh de entrada variable (VEKM, 1983) por Ali M. Rushdi (1951-),[97] [98] [99] [100] [101] [102] [96] mapa de entrada variable (VEM) de William I. Fletcher (1938-2020) [91] [103] o mapa de entrada variable (VEM ) [104]

- Método del hipercubo (1982) de Stamatios V. Kartalopoulos [105]

- Mapa de anillo mínimo (MRM) o algoritmo de anillo mínimo (1990) de Thomas R. McCalla [106] [95] [107] [103]

- Diagrama V (2001) de Jonathan Westphal (1951–) [108] [109]

- Paraboomig (2003) de Shrish Verma y Kiran D. Permar [110] [111]

- Gráfico de inversor mayoritario (MIG) (2014) de Luca Amarú, Pierre-Emmanuel Gaillardon y Giovanni De Micheli [112] [113]

- Trama de Pandit (2017) de Vedhas Pandit y Björn W. Schuller (1975–) [114]

- Gráfico de la verdad (2020) de Eisa Alharbi [115] [116]

Ver también

- Diagrama de decisión binaria (BDD)

- No me importa la condición

- Primer implicante

- Complejidad del circuito

- Composición de funciones

- Descomposición de funciones

- Subutilización de la puerta

- Gráfico de minimización de Harvard (Wikiversidad) (Wikilibros)

Referencias

- ^ Buchführer, David; Umans, Christopher (enero de 2011). "La complejidad de la minimización de fórmulas booleanas" (PDF) . Revista de Ciencias de la Computación y Sistemas (JCSS) . Departamento de Ciencias de la Computación, Instituto de Tecnología de California , Pasadena, California, EE. UU .: Elsevier Inc. 77 (1): 142–153. doi : 10.1016 / j.jcss.2010.06.011 .Ésta es una versión ampliada del documento de la conferencia: Buchführer, David; Umans, Christopher (2008). "La complejidad de la minimización de fórmulas booleanas". Actas de Autómatas, Lenguajes y Programación (PDF) . 35º Coloquio Internacional (ICALP) . Lecture Notes in Computer Science (LNCS). 5125 . Berlín / Heidelberg, Alemania: Springer-Verlag . págs. 24–35. doi : 10.1007 / 978-3-540-70575-8_3 . ISBN 978-3-540-70574-1. Archivado (PDF) desde el original el 14 de enero de 2018 . Consultado el 14 de enero de 2018 .

- ^ Nelson, Raymond J. (junio de 1955). "Funciones de verdad normales más simples". Revista de lógica simbólica . Asociación de Lógica Simbólica . 20 (2): 105–108. doi : 10.2307 / 2266893 . JSTOR 2266893 . (4 páginas) (NB. Un método que convierte una forma normal conjuntiva en una forma normal disyuntiva , seguido de un procedimiento similar al de Quine ).

- ^ Nelson, Raymond J. (septiembre de 1955). "Funciones de verdad normales más simples y débiles". Revista de lógica simbólica . Asociación de Lógica Simbólica . 20 (3): 232–234. doi : 10.2307 / 2268219 . JSTOR 2268219 . (3 páginas)

- ^ Lipp, Hans Martin; Becker, Jürgen (2011). Grundlagen der Digitaltechnik (en alemán) (reelaborado en la 7ª ed.). Múnich, Alemania: Oldenbourg Wissenschaftsverlag GmbH / Walter de Gruyter . ISBN 9783486706932. ISBN 3486706934 . Consultado el 12 de mayo de 2020 . (316 páginas)

- ^ Riznyk, Volodymyr; Solomko, Mykhailo (julio de 2017). "Minimización de funciones booleanas por método combinatorio" . Sistemas de información y control: Modelización matemática (en inglés y ruso). 4/2 (36): 49–64. doi : 10.15587 / 2312-8372.2017.108532 . ISSN 2226-3780 . UDC 681.325. Archivado (PDF) desde el original el 12 de mayo de 2020 . Consultado el 12 de mayo de 2020 .

- ^ Riznyk, Volodymyr; Solomko, Mykhailo (julio de 2018). "Minimización de formas conductivas normales de funciones booleanas por método combinatorio" (PDF) . Sistemas de información y control: Modelización matemática (en inglés y ruso). 5/2 (43): 42–55. doi : 10.15587 / 2312-8372.2018.146312 . ISSN 2226-3780 . UDC 681.325. Archivado (PDF) desde el original el 12 de mayo de 2020 . Consultado el 12 de mayo de 2020 .

- ↑ Roth, John Paul (julio de 1959) [5 de abril de 1957]. "Métodos topológicos algebraicos en síntesis". Actas de un Simposio Internacional sobre la Teoría de Conmutación, Parte I . Los Anales del Laboratorio de Computación de Harvard. Cambridge, Massachusetts, Estados Unidos: Harvard University Press . XXIX : 57–73.

- ^ Roth, John Paul (julio de 1958). "Métodos topológicos algebraicos para la síntesis de sistemas de conmutación, parte I" . Transacciones de la American Mathematical Society . 88 (2): 301–326. doi : 10.2307 / 1993216 . JSTOR 1993216 . (26 páginas)

- ^ Roth, John Paul (noviembre de 1960). "Minimización sobre árboles booleanos". Revista de investigación y desarrollo de IBM . 4 (5): 543–558. doi : 10.1147 / rd.45.0543 . eISSN 0018-8646 . ISSN 0018-8646 .

- ^ Kudielka, Viktor; Camina, Kurt; Bandat, Kurt; Lucas, Peter ; Zemanek, Heinrich "Heinz" Josef (29 de febrero de 1960). "4-5". En Zemanek, Heinrich "Heinz" Josef (ed.). Programas de procesamiento de datos lógicos . Mailüfterl (Informe final). Viena, Austria: Universidad Técnica de Viena , Institut für Nachrichtentechnik. Contrato de la Oficina Europea de Investigación DA-91-591-EC-1062 . Consultado el 29 de mayo de 2020 . (198 páginas)

- ^ Kudielka, Viktor; Lucas, Peter ; Camina, Kurt; Bandat, Kurt; Bekic, Heinz; Zemanek, Heinrich "Heinz" Josef (31 de julio de 1961). "2". Ampliación del lenguaje algorítmico ALGOL (Informe final). Contrato de la Oficina Europea de Investigación DA-91–591-EUC-1430.

- ↑ Kudielka, Viktor (enero de 1963) [18 de octubre de 1961]. "Programmierung von Minimisierungsverfahren für zweistufige Logik" . En Dörr, Johannes; Peschl, Ernst Ferdinand ; Unger, Heinz (eds.). 2. Coloquio sobre Schaltkreis- und Schaltwerk-Theorie - Vortragsauszüge vom 18. bis 20. Oktober 1961 en Saarbrücken . Internationale Schriftenreihe zur Numerischen Mathematik [Serie internacional de matemáticas numéricas] (ISNM) (en alemán). 4 (reimpresión del 20/12/2013 de la 1ª ed.). Institut für Angewandte Mathematik, Universität Saarbrücken , Rheinisch-Westfälisches Institut für Instrumentelle Mathematik: Springer Basel AG / Birkhäuser Verlag Basel. págs. 49–65. doi : 10.1007 / 978-3-0348-4156-6 . ISBN 978-3-0348-4081-1. Consultado el 15 de abril de 2020 . (152 páginas)

- ^ Wells, Mark B. (1962). "Capítulo 14. Teoría de conmutación: aplicación de un teorema de cobertura de conjuntos finitos a la simplificación de expresiones de funciones booleanas" . Procesamiento de información, Actas del 2do Congreso IFIP 1962, Munich, Alemania, 27 de agosto - 1 de septiembre de 1962 . 2 . Munich, Alemania: Holanda Septentrional . págs. 731–735 . Consultado el 28 de mayo de 2020 .

- ↑ Scheinman, Arnold H. (julio de 1962) [6 de marzo de 1962]. "Un método para simplificar funciones booleanas" . Revista técnica de Bell System . Nokia Bell Labs . 41 (4): 1337-1346. doi : 10.1002 / j.1538-7305.1962.tb03280.x . ISSN 0005-8580 . [1] (NB. También conocido como método binario de Scheinman , este es un método iterativo fácil de usar también para funciones grandes, lo que resultará en funciones significativamente simplificadas, pero no necesariamente en las más simples. El autor a veces se escribe mal como "Schienmann" .)

- ↑ a b Föllinger, Otto ; Weber, Wolfgang (1967) [junio de 1965]. "5.4. Die Methode der Harvard Group of Computation / 5.5 Vereinfachungsmethode nach Scheinman". Escrito en Frankfurt am Main, Alemania. Methoden der Schaltalgebra (en alemán) (1 ed.). Múnich, Alemania: R. Oldenbourg Verlag . págs. 103, 120, 122-128, 128-135. (6 + 320 + 6 páginas)

- ^ Mano, M. Morris; Kime, Charles R. (2014). Fundamentos de diseño lógico y informático (4ª nueva ed. Internacional). Pearson Education Limited . pag. 54. ISBN 978-1-292-02468-4.

- ^ Venn, John (julio de 1880). "I. Sobre la representación esquemática y mecánica de proposiciones y razonamientos" (PDF) . The London, Edinburgh y Dublin Philosophical Magazine y Journal of Science . 5. 10 (59): 1–18. doi : 10.1080 / 14786448008626877 . Archivado (PDF) desde el original el 16 de mayo de 2017. [2] [3]

- ↑ Venn, John (1880). "Sobre el empleo de diagramas geométricos para las representaciones sensibles de proposiciones lógicas" . Actas de la Sociedad Filosófica de Cambridge . 4 : 47–59.

- ^ Marquand, Allan (1881). "XXXIII: en diagramas lógicos para n términos". The London, Edinburgh y Dublin Philosophical Magazine y Journal of Science . 5. 12 (75): 266–270. doi : 10.1080 / 14786448108627104 .(NB. Muchas fuentes secundarias citan erróneamente este trabajo como "Un diagrama lógico para n términos" o "En un diagrama lógico para n términos".)

- ↑ a b Brown, Frank Markham (2012) [2003, 1990]. Razonamiento booleano - La lógica de las ecuaciones booleanas (reedición de la 2ª ed.). Mineola, Nueva York: Dover Publications, Inc. ISBN 978-0-486-42785-0. ISBN 0-486-42785-4 . PDF de la primera edición

- ^ Aiken, Howard Hathaway ; Blaauw, Gerrit Anne ; Burkhart, William; Burns, Robert J .; Cali, Lloyd; Canepa, Michele; Ciampa, Carmela M .; Coolidge, Jr., Charles A .; Fucarile, Joseph R .; Gadd, Jr., J. Orten; Gucker, Frank F .; Harr, John A .; Hawkins, Robert L .; Hayes, Miles V .; Hofheimer, Richard; Hulme, William F .; Jennings, Betty L .; Johnson, Stanley A .; Kalin, Theodore; Kincaid, Marshall; Lucchini, E. Edward; Minty, William; Moore, Benjamin L .; Remmes, Joseph; Rinn, Robert J .; Roche, John W .; Sanbord, Jacquelin; Semon, Warren L .; Cantante, Theodore; Smith, Dexter; Smith, Leonard; Strong, Peter F .; Thomas, Helene V .; Wang, An; Whitehouse, Martha L .; Wilkins, Holly B .; Wilkins, Robert E .; Woo, Way Dong; Little, Elbert P .; McDowell, M. Scudder (1952) [enero de 1951]. "Capítulo V: Minimización de gráficos". Síntesis de circuitos electrónicos de computación y control . Los Anales del Laboratorio de Computación de la Universidad de Harvard. XXVII (segunda impresión, edición revisada). Base de la Fuerza Aérea Write-Patterson: Harvard University Press (Cambridge, Massachusetts, EE. UU.) / Geoffrey Cumberlege Oxford University Press (Londres). pp. prefacio, 50–67. arca: / 13960 / t4zh1t09d . Consultado el 16 de abril de 2017 . pag. prefacio:

[…] Martha Whitehouse elaboró los gráficos de minimización que se utilizan con tanta profusión a lo largo de este libro y, además, preparó gráficos de minimización de siete y ocho variables con fines experimentales. […] Por lo tanto, el presente autor está obligado a dejar constancia de que el enfoque algebraico general, la función de conmutación, el operador del tubo de vacío y la tabla de minimización son sus propuestas, y que él es responsable de su inclusión aquí. […]

(2 + x + 278 + 2 páginas) (NB. El trabajo comenzó en abril de 1948.) - ↑ a b Karnaugh, Maurice (noviembre de 1953) [23 de abril de 1953, 17 de marzo de 1953]. "El método de mapa para la síntesis de circuitos lógicos combinacionales" (PDF) . Transacciones del Instituto Americano de Ingenieros Eléctricos, Parte I: Comunicación y Electrónica . 72 (5): 593–599. doi : 10.1109 / TCE.1953.6371932 . Documento 53-217. Archivado desde el original (PDF) el 16 de abril de 2017 . Consultado el 16 de abril de 2017 .

- ^ Phister, Jr., Montgomery (abril de 1959) [diciembre de 1958]. Diseño lógico de computadoras digitales . Diseño y aplicaciones digitales (3ª edición, 1ª ed.). Nueva York, Estados Unidos: John Wiley & Sons Inc. págs. 75–83. ISBN 0-47168805-3. LCCN 58-6082 . Señor 0093930 . ISBN 978-0-47168805-1 . (xvi + 408 páginas)

- ↑ a b c Curtis, Herbert Allen (1962). Un nuevo enfoque para el diseño de circuitos de conmutación . The Bell Laboratories Series (1 ed.). Princeton, Nueva Jersey, EE. UU .: D. van Nostrand Company, Inc. ISBN 0-44201794-4. OCLC 1036797958 . S2CID 57068910 . ISBN 978-0-44201794-1 . arca: / 13960 / t56d6st0q. (viii + 635 páginas) (NB. Este libro fue reimpreso por Chin Jih en 1969.)

- ↑ Ashenhurst, Robert "Bob" Lovett (enero de 1953) [1 de septiembre de 1952, 1 de enero de 1953]. "La descomposición de las funciones de conmutación". Informe de Bell Laboratories (informe). Laboratorio de Computación de Harvard , Universidad de Harvard, Cambridge, Massachusetts, Estados Unidos: Bell Laboratories (BL-1): II-1 – II-37. PB122812.(37 de 98 páginas) (NB. Este artículo fue reimpreso en el apéndice de Curtis (1962) , pp. 571–602.); otro artículo del mismo título fue publicado como: Ashenhurst, Robert "Bob" Lovett (diciembre de 1956) [1956-05-01, 1956-12-01]. Aiken, Howard Hathaway (ed.). "La descomposición de las funciones de conmutación". Informe de Bell Laboratories / Teoría de la conmutación (informe). Laboratorio de Computación de Harvard , Universidad de Harvard, Cambridge, Massachusetts, Estados Unidos: Bell Laboratories (BL-16): III-1-III-72. PB147348.(72 de 193 páginas); Posteriormente se publicó un artículo actualizado con el mismo título que: Ashenhurst, Robert "Bob" Lovett (1957-04-02). "La descomposición de las funciones de conmutación" (PDF) . Actas del Simposio Internacional sobre la Teoría de Conmutación, Parte I . Los Anales del Laboratorio de Computación de la Universidad de Harvard. Universidad de Harvard, Cambridge, Massachusetts, EE.UU .: Harvard University Press (publicado en 1959). XXIX : 74-116. Archivado (PDF) desde el original el 28 de marzo de 2021 . Consultado el 29 de marzo de 2021 . (43 páginas)

- ↑ Singer, Theodore "Ted" (julio de 1953) [1 de abril de 1953, 1 de julio de 1953]. "La tabla de descomposición como ayuda teórica". Informe de Bell Laboratories (informe). Laboratorio de Computación de Harvard , Universidad de Harvard, Cambridge, Massachusetts, Estados Unidos: Bell Laboratories (BL-4): III-1 – III-28. PB122815.(28 de 149 páginas) (NB. Este artículo se reimprimió en el apéndice de Curtis (1962) , págs. 602–620.)

- ↑ Ashenhurst, Robert "Bob" Lovett (julio de 1953) [1 de abril de 1953, 1 de julio de 1953]. "Descomposición no disjunta". Informe de Bell Laboratories (informe). Laboratorio de Computación de Harvard , Universidad de Harvard, Cambridge, Massachusetts, Estados Unidos: Bell Laboratories (BL-4): IV-1 – IV-12. PB122815.(12 de 149 páginas) (NB. Este artículo fue reimpreso en el apéndice de Curtis (1962) , págs. 620–630.)

- ↑ Veitch, Edward Westbrook (3 de mayo de 1952) [2 de mayo de 1952]. "Un método de gráfico para simplificar las funciones de la verdad". Transacciones de la Reunión Anual de la ACM de 1952 . Conferencia anual / Reunión anual de la ACM: Actas de la reunión anual de la ACM de 1952 (Pittsburgh, Pensilvania, EE. UU.). Nueva York, Estados Unidos: Asociación de Maquinaria de Computación (ACM): 127-133. doi : 10.1145 / 609784.609801 .

- ↑ Svoboda, Antonín (27 de noviembre de 1955) [22 de noviembre de 1955]. Graphisch-mechanische Hilfsmittel für die Synthese von Relaisschaltungen [ Ayudas gráfico-mecánicas para la síntesis de circuitos de relé ] (Informe). Dresde, Alemania: Internationales Mathematiker-Kolloquium über aktuelle Probleme der Rechentechnik. págs. 43–50.(NB. Según Constantinescu, el contenido podría ser idéntico al de un artículo de una revista en 1956.)

- ^ Svoboda, Antonín (1956). Graficko-mechanické pomůcky užívané při analizar una síntesis kontaktových obvodů [ Utilización de ayudas gráfico-mecánicas para el análisis y síntesis de circuitos de contacto ]. Stroje na zpracování informací [ Simposio sobre máquinas de procesamiento de información ] (en checo). IV . Praga: Academia de Ciencias de Checoslovaquia, Instituto de Investigación de Máquinas Matemáticas. págs. 9-22.Mantenimiento CS1: fecha y año ( enlace )

- ^ Svoboda, Antonín (1956). (desconocido) [ Ayudas gráfico-mecánicas para la síntesis de circuitos de relés ]. Nachrichtentechnische Fachberichte (NTF), Beihefte der Nachrichtentechnischen Zeitschrift (NTZ) (en checo). 4 . Braunschweig, Alemania: Friedrich Vieweg & Sohn . págs. 213–218. ECIP55 213. Cite usa un título genérico ( ayuda ) (NB. Según Constantinescu, el contenido podría ser idéntico a un informe del congreso en 1955.)Mantenimiento CS1: fecha y año ( enlace )

- ↑ Svoboda, Antonín (1959) [29/03/1957]. "Algunas aplicaciones de las rejillas de contactos". Actas de un Simposio Internacional sobre la Teoría de la conmutación, 2-5 de abril de 1957, Parte I . Los Anales del Laboratorio de Computación de la Universidad de Harvard. XXIX . Universidad de Harvard, Cambridge, Massachusetts, EE.UU .: Harvard University Press . págs. 293-305. (305 páginas)

- ^ Svoboda, Antonín (1958). (desconocido) [ Ayudas gráficas para la minimización en circuitos de conmutación ]. Stroje na zpracování informací [ Simposio sobre máquinas de procesamiento de información ] (en checo). VI . Praga: Academia de Ciencias de Checoslovaquia, Instituto de Investigación de Máquinas Matemáticas. págs. 35–53. Citar utiliza un título genérico ( ayuda )

- ^ McNaughton, Robert Forbes (marzo de 1958). "Antonin Svoboda. Ayudas gráfico-mecánicas para la síntesis de circuitos de relés. Aktuelle Probleme der Rechentechnik, Deutscher Verlag der Wissenschaften, Berlín 1957, págs. 43–50" . Revista de lógica simbólica (Revisión). 23 (1): 60–61. doi : 10.2307 / 2964502 . Consultado el 14 de mayo de 2020 . pag. 60:

Las dos ayudas gráfico-mecánicas son huesos de contacto y rejillas de contacto. Los huesos de contacto son una ayuda para analizar (es decir, encontrar una fórmula lógica para) las redes de contactos. La teoría lógica del análisis de redes de contactos se ha entendido en general desde hace mucho tiempo, pero existen dificultades prácticas, especialmente en el análisis de redes puente (es decir, redes que no son del tipo serie-paralelo). Las cuadrículas de contactos son una ayuda para obtener una fórmula normal para funciones dadas en forma de tabla de verdad. Son útiles para obtener lo que otros llaman implicantes primos. […]

(NB. Esta revisión es sobre el informe del congreso de Svoboda ). - ↑ Constantinescu, Paul (22 de diciembre de 1959). "Svoboda, Antonin. Ayudas gráfico-mecánicas para la síntesis de circuitos de relés. Elektronische Rechenmaschinen und Informationsverarbeitung, 213-218 (1956). - Ber. Internat. Math.-Kolloquium Dresden, 22. bis 27. Nov. 1955, 42– 50 (1957) " . Zentralblatt für Mathematik (Revisión). 82 (1): 126. Zbl 0082.12602 . Archivado desde el original el 14 de mayo de 2020 . Consultado el 14 de mayo de 2020 . pag. 126:

El autor utiliza ayudas mecánicas interesantes para resolver problemas relacionados con las redes de contactos. La base para la creación de estas ayudas es el hecho de que cada variable independiente puede expresarse mediante una suma booleana de variables que definen el estado de la red. Empleando "huesos de contacto" y "cuadrículas de contacto" el autor logra el análisis y síntesis de una red de contactos y la transformación de las funciones booleanas dadas en forma tabular en forma algebraica.

(NB. Esta revisión es sobre el informe del congreso y el artículo de revista de Svoboda ). - ↑ a b Roginskij [Рогинский], Vadim Nikolaevich [Вадим Николаевич] (1962). Grundlagen der Struktursynthese von Relaisschaltungen (en alemán). Traducido por Hausenblas, Albin; Pfaffinger, Robert; Resele, H. (1ª ed. Alemana). Múnich, Alemania: R. Oldenbourg Verlag . OCLC 968499019 . OCLC 163791522 . Consultado el 30 de mayo de 2002. (204 páginas). Este libro es una traducción del trabajo original: Roginskij [Рогинский], Vadim Nikolaevich [Вадим Николаевич] (1959). Kharkevich [Харкевич], Aleksandr Aleksandrovich [Александр Александрович] (ed.). Ėlementy strukturnogo sinteza releĭnykh skhem upravlenii︠a︡ Элементы структурного синтеза релейных схем управления(en ruso) (1ª ed.). Moscú: Изд-во Академии наук СССР (Izdatel'stvo akademii nauk SSSR) [4] . También disponible en inglés como: Roginskij [Рогинский], Vadim Nikolaevich [Вадим Николаевич] (1963). La síntesis de circuitos de conmutación de relés . Traducido por Chrzczonowicz (1ª ed. En inglés). Nueva York, EE. UU .: Van Nostrand Reinhold Inc. ISBN 0-44207020-9. (188 páginas).

- ^ Svoboda, Antonín (1960). Análisis de funciones booleanas mediante tarjetas lógicas perforadas . Stroje na zpracování informací [ Simposio sobre máquinas de procesamiento de información ]. VII . págs. 13-20.

- ↑ Svoboda [Свобода], Antonín [Антони́н] (2 de febrero de 1961).Некоторые способы применения контактных сеток[Algunas aplicaciones de las cuadrículas de contactos] (PDF) . Avtomatika i Telemekhanika Автоматика и Телемеханика[ Automatización y control remoto ] (en ruso). XXII (8): 1061–1107. Mi at12365 . Archivado desde el original el 19 de mayo de 2020 . Consultado el 16 de mayo de 2020 . [5] (11 páginas)

- ^ Svoboda, Antonín (diciembre de 1969). "Instrumentos lógicos para la enseñanza del diseño lógico". Transacciones IEEE sobre educación . IEEE . E-12 (4): 262–273. doi : 10.1109 / TE.1969.4320517 . eISSN 1557-9638 . ISSN 0018-9359 .

- ^ Klír, George Jiří ; Seidl, Lev K. (1968) [1966]. Ainsworth, WA (ed.). Síntesis de circuitos de conmutación . Traducido por Dolan, Pavel (1ª ed. En inglés). Londres, Reino Unido: Iliffe Books Ltd. / (SNTL Publishers of Technical Literature, Praga). págs. 62–66, 69–75, 199–204. (325 + 1 páginas)

- ↑ a b Steinbuch, Karl W .; Weber, Wolfgang; Heinemann, Traute, eds. (1974) [1967]. Taschenbuch der Informatik - Band II - Struktur und Programmierung von EDV-Systemen . Taschenbuch der Nachrichtenverarbeitung (en alemán). 2 (3 ed.). Berlín, Alemania: Springer-Verlag . págs. 25, 62, 96, 122-123, 238. ISBN 3-540-06241-6. LCCN 73-80607 .

- ^ Svoboda, Antonín ; White, Donnamaie E. (2016) [2012, 1985, 1 de agosto de 1979]. Técnicas avanzadas de diseño de circuitos lógicos (PDF) (reedición electrónica reescrita ed.). Garland STPM Press (edición original) / WhitePubs Enterprises, Inc. (reedición). ISBN 0-8240-7014-3. LCCN 78-31384 . ISBN 978-0-8240-7014-4 . Archivado (PDF) desde el original el 15 de marzo de 2016 . Consultado el 15 de abril de 2017 . [6] [7]

- ^ Вадим Николаевич Рогинский (некролог)[Vadim Nikolaevich Roginsky (obituario)]. Problemy Peredachi Informatsii Проблемы передачи информации[ Problemas de transmisión de información ] (en ruso). XIX (3): 111. 1983. ISSN 0555-2923 . Mi ppi1195 . Archivado desde el original el 29 de mayo de 2020 . Consultado el 29 de mayo de 2020 . [8] (NB. El nombre del autor ( GND 1157173993 , 1158776373 ) a veces se traduce como "Vladimir Nikolaevič", "Wladimir Nikolajewitsch" y como "Roginsky", "Roginskiĭ" o "Roginski".)

- ^ Roginskij [Рогинский], Vadim Nikolaevich [Вадим Николаевич] (1957). "(desconocido)" [Método gráfico para sintetizar redes de contactos]. Èlektrosvâzʹ (en ruso). XI (11): 82–88. ISSN 0013-5771 . Citar utiliza un título genérico ( ayuda )

- ↑ Roginskij [Рогинский], Vadim Nikolaevich [Вадим Николаевич] (1959) [29 de marzo de 1957]. "Un método gráfico para la síntesis de redes de contactos multiterminal". Actas de un simposio internacional sobre la teoría de la conmutación, 2 a 5 de abril de 1957, Parte II . Los Anales del Laboratorio de Computación de la Universidad de Harvard. XXX . Universidad de Harvard, Cambridge, Massachusetts, Estados Unidos. págs. 302–315. (345 páginas) (NB. Esta es una traducción de un documento en ruso preparado para el simposio. Roginskij envió el documento para su presentación, pero luego no pudo asistir personalmente. La traducción fue realizada por algunos de los asistentes estadounidenses).

- ↑ Roginskij [Рогинский], Vadim Nikolaevich [Вадим Николаевич] (1958). Povarov [Поваров], Gellius Nikolaevich [Геллий Николаевич] (ed.). "(desconocido)" [Método gráfico para sintetizar redes de contactos multiterminal]. Avtomatika [ Automatización ] (en ruso). Kiev. 3 : 84–91. ISSN 0572-2691 . Citar utiliza un título genérico ( ayuda )

- ↑ Händler, Wolfgang (19 de diciembre de 1958). Ein Minimisierungsverfahren zur Synthese von Schaltkreisen (Minimisierungsgraphen) (Disertación) (en alemán). Potsdam, Alemania: Technische Hochschule Darmstadt . D 17.(73 páginas + aplicación) [9]

- ^ Händler, Wolfgang (2013) [junio de 1961, 26 de octubre de 1960]. "Zum Gebrauch von Graphen in der Schaltkreis- und Schaltwerktheorie". En Peschl, Ernst Ferdinand ; Unger, Heinz (eds.). Coloquio sobre Schaltkreis- und Schaltwerk-Theorie - Vortragsauszüge vom 26. bis 28. Oktober 1960 en Bonn . Internationale Schriftenreihe zur Numerischen Mathematik [Serie internacional de matemáticas numéricas] (ISNM) (en alemán). 3 . Institut für Angewandte Mathematik, Universität Saarbrücken , Rheinisch-Westfälisches Institut für Instrumentelle Mathematik: Springer Basel AG / Birkhäuser Verlag Basel . págs. 169–198. doi :10.1007 / 978-3-0348-5770-3_10 . ISBN 978-3-0348-5771-0. ISBN 3-0348-5771-3 . (198 páginas)

- ↑ Berger, Erich R .; Händler, Wolfgang (1967) [1962]. Steinbuch, Karl W .; Wagner, Siegfried W. (eds.). Taschenbuch der Nachrichtenverarbeitung (en alemán) (2 ed.). Berlín, Alemania: Springer-Verlag OHG . págs. 64, 1034-1035, 1036, 1038. LCCN 67-21079 . Título No. 1036. p. 64:

[…] Übersichtlich ist die Darstellung nach

Händler

, die sämtliche Punkte, numeriert nach dem

Gray-Code

[…], auf dem Umfeld eines Kreises anordnet. Sie erfordert allerdings sehr viel Platz. […]

[ Ilustración de Händler , donde todos los puntos, numerados según el código Gray, están dispuestos en la circunferencia de un círculo, es fácilmente comprensible. Sin embargo, necesita mucho espacio.]

- ^ Dokter, Folkert; Steinhauer, Jürgen (18 de junio de 1973). "3.7.1. Diagrama de Händler" . Electrónica digital . Biblioteca técnica de Philips (PTL) / Macmillan Education (Reimpresión de la 1ª edición en inglés). Eindhoven, Países Bajos: The Macmillan Press Ltd. / NV Philips 'Gloeilampenfabrieken . págs. 108-111. doi : 10.1007 / 978-1-349-01417-0 . ISBN 978-1-349-01419-4. SBN 333-13360-9. Consultado el 11 de mayo de 2020 . (270 páginas) (NB. Se basa en una traducción del volumen I de la edición alemana en dos volúmenes).

- ^ Dokter, Folkert; Steinhauer, Jürgen (1975) [1969]. "3.7.1. Kreisgraphen nach Händler". Digitale Elektronik in der Meßtechnik und Datenverarbeitung: Theoretische Grundlagen und Schaltungstechnik . Philips Fachbücher (en alemán). I (mejorada y ampliada 5ª ed.). Hamburgo, Alemania: Deutsche Philips GmbH . págs. 115, 124, 129, 130-134 [130-134]. ISBN 3-87145-272-6. (xii + 327 + 3 páginas) (NB. La edición alemana del volumen I se publicó en 1969, 1971, dos ediciones en 1972 y 1975. El volumen II se publicó en 1970, 1972, 1973 y 1975.)

- ↑ Klar, Rainer (1 de febrero de 1970). "2.4.2 Graphische Minimisierungsverfahren" [2.4.2 Métodos gráficos de minimización]. Digitale Rechenautomaten - Eine Einführung [ Computadoras digitales - Introducción ]. Sammlung Göschen (en alemán). 1241 / 1241a (1 ed.). Berlín, Alemania: Walter de Gruyter & Co. / GJ Göschen'sche Verlagsbuchhandlung . págs. 70–73. ISBN 3-11-083160-0. ISBN 978-3-11-083160-3 . Archiv-Nr. 7990709. Archivado desde el original el 13 de abril de 2020 . Consultado el 13 de abril de 2020 . págs. 70–72:

[…] Der Kreisgraph nach Händler ordnet den einzelnen

Mintermen Knoten

eines Graphen zu. Die Nachbarschaft von Mintermen wird durch Kanten dargestellt, die die entsprechenden Knoten miteinander verbinden. Bei dem "Kreisgraph" liegen sämtliche Knoten auf einem Kreis. Um symmetrische Kanten zu bekommen, wird die Reihenfolge der Knoten (bzw. Minterme) durch den

reflektierten Gray-Code

festgelegt, der sich durch fortlaufende Spiegelung und Ergänzung konstruieren läßt. Die negierten Variablen werden dabei durch Nullen, die nichtnegierten durch Einsen dargestellt. Man beginnt mit einer Variablen, die negiert (0) oder nichtnegiert (1) auftritt. Die 0 und 1 werden gespiegelt. Durch Anfügen einer Null vor 0 und 1 und einer Eins vor die Spiegelbilder werden Terme mit 2 Variablen gebildet. Die Spiegelung und das Anfügen von Nullen und Einsen wird wiederholt, bis die gewünschte Zahl von n Variablen und 2 nTermen erreicht ist. […] Das Minimisierungsverfahren mit dem Kreisgraphen verläuft in folgenden Schritten: I. Aufstellung der DKF [Disjunktive kanonische Form]. II. Alle Knoten, die auftretende Minterme repräsentieren, werden gekennzeichnet. III. Alle Kanten, die markierte Knoten verbinden, werden gekennzeichnet. Der so entstandene Untergraph markiert sämtliche Primimplikanten . Er setzt sich zusammen aus folgenden Unterstrukturen: isolierten Knoten (Primimplikant der Länge n), 2 1 verbundenen Knoten (Primimplikant der Länge n − 1), 2 2 verbundenen Knoten (Primimplikant der Länge n − 2), 2 3verbundenen Knoten (Primimplikant der Länge n − 3) usw. Das Auffinden der wesentlichen Primimplikanten und der Restüberdeckung bleibt wie beim Karnaugh-Veitch-Diagramm der Geschicklichkeit überlassen. […]

(205 páginas) (NB. Una reimpresión de 2019 de la primera edición está disponible bajo ISBN 3-11002793-3 , 978-3-11002793-8 . También existe una cuarta edición reelaborada y ampliada ). - ↑ Klar, Rainer (1989) [1 de octubre de 1988]. "2.4.2 Graphische Minimisierungsverfahren" [2.4.2 Métodos gráficos de minimización]. Digitale Rechenautomaten - Eine Einführung in die Struktur von Computerhardware [ Computadoras digitales - Introducción a la estructura del hardware de computadora ]. Sammlung Göschen (en alemán). 2050 (cuarta edición revisada). Berlín, Alemania: Walter de Gruyter & Co. págs. 94–97. ISBN 3-11011700-2. ISBN 978-3-11011700-4 . (320 páginas)

- ^ Hotz, Günter (1974). Schaltkreistheorie [ Teoría del circuito de conmutación ]. DeGruyter Lehrbuch (en alemán) (1 ed.). Walter de Gruyter & Co. p. 117. ISBN 3-11-00-2050-5. Archivado desde el original el 13 de abril de 2020 . Consultado el 13 de abril de 2020 . pag. 117:

[…] Der Kreisgraph von Händler ist für das Auffinden von Primimplikanten gut brauchbar . Er hat den Nachteil, daß er schwierig zu zeichnen ist. Diesen Nachteil kann man allerdings durch die Verwendung von Schablonen verringern. […]

[El gráfico circular de Händler es muy adecuado para encontrar implicantes primos . Una desventaja es que es difícil de dibujar. Esto se puede remediar usando plantillas.] - ^ "Informatik Sammlung Erlangen (ISER)" (en alemán). Erlangen, Alemania: Friedrich-Alexander Universität . 2012-03-13. Archivado desde el original el 16 de mayo de 2017 . Consultado el 12 de abril de 2017 .(NB. Muestra una imagen de un Kreisgraph de Händler .)

- ^ "Informatik Sammlung Erlangen (ISER) - Impressum" (en alemán). Erlangen, Alemania: Friedrich-Alexander Universität . 2012-03-13. Archivado desde el original el 26 de febrero de 2012 . Consultado el 15 de abril de 2017 .(NB. Muestra una imagen de un Kreisgraph de Händler .)

- ^ Zemanek, Heinrich "Heinz" Josef (2013) [1990]. "Geschichte der Schaltalgebra" [Historia del álgebra de conmutación de circuitos]. En Broy, Manfred (ed.). Informatik und Mathematik [ Ciencias de la Computación y Matemáticas ] (en alemán). Springer-Verlag . págs. 43–72. doi : 10.1007 / 978-3-642-76677-0_3 . ISBN 9783642766770. ISBN 3642766773 . pag. 58:

Einen Weg besonderer Art, der damals zu wenig beachtet wurde, wies

W. Händler

in seiner Disertación […] mit einem Kreisdiagramm.

[…]

(NB. Colección de trabajos en un coloquio celebrado en la Bayerische Akademie der Wissenschaften , 1989-06-12 / 14, en honor a Friedrich L. Bauer .) - ^ Bauer, Friedrich Ludwig ; Wirsing, Martin (marzo de 1991). Elementare Aussagenlogik (en alemán). Berlín / Heidelberg: Springer-Verlag . págs. 54–56, 71, 112–113, 138–139. ISBN 3-540-52974-8. ISBN 978-3-540-52974-3 . pag. 54:

[…] handelt es sich um ein

Händler

-Diagramm […], mit den Würfelecken als Ecken eines 2

m

-gons. […] Abb. […] Zeigt auch Gegenstücke für andere Dimensionen. Durch waagerechte Linien sind dabei Tupel verbunden, die sich nur in der ersten Komponente unterscheiden; durch senkrechte Linien solche, die sich nur in der zweiten Komponente unterscheiden; durch 45 ° -Linien und 135 ° -Linien solche, die sich nur in der dritten Komponente unterscheiden usw. Als Nachteil der Händler-Diagramme wird angeführt, daß sie viel Platz beanspruchen. […]

- ^ Peticolas, Alfred B .; Mahoney, Matthew V. (20 de diciembre de 1963). Circuitos informáticos y sistemas informáticos (Manual de laboratorio). Nueva York, Estados Unidos: RCA Institutes, Inc. C-15. A674036.(NB. Este trabajo formó la base del manual del curso de 1964 ).

- ^ Peticolas, Alfred B .; Mahoney, Matthew V. (10 de agosto de 1964). Diseño lógico para sistemas digitales . Nueva York, Estados Unidos: RCA Institutes, Inc. A715535. N65-25354. [10] [11] (191 + 1 páginas) (NB. Este manual del curso se basa en el manual de laboratorio de 1963 ).

- ^ Peticolas, Alfred B .; Mahoney, Matthew V .; Laguzzi, Mario C., eds. (8 de mayo de 1967) [1966]. Diseño lógico (notas de clase) (4 ed.). Nueva York, Estados Unidos: RCA Institutes, Inc. A917290.(185 páginas) (NB. Esta cuarta edición de una carpeta para estudiantes del curso, basada en el manual anterior , se menciona en un volante de la RCA de 1968 ).

- ^ Escuela de programa educativo personalizado (22 de julio de 1966). Diseño lógico (volante). Nueva York, Estados Unidos: RCA Institutes, Inc. CE-105-R56. arca: / 13960 / t56f22q9v . Consultado el 20 de febrero de 2021 .

[…] Personal […] Bradford Daggett, Director […] Matthew V. Mahoney, Admin., Desarrollo […] Alfred B. Peticolas, Decano […] Mario C. Laguzzi, Miembro del Equipo Técnico […] Edward K. Marrie, miembro del personal técnico […] Abraham Schwartz, miembro del personal técnico […]

[12] - ^ "Diseño lógico: desarrollo del mapa de Mahoney". Escrito en Syracuse, Nueva York, EE. UU. Un plan de estudios sobre el contenido del diseño lógico: un seminario educativo de cinco días para ingenieros presentado por los institutos RCA (folleto). Nueva York, Estados Unidos: RCA Institutes, Inc. 1968-11-25. arca: / 13960 / t8kd8cx8z . Consultado el 20 de febrero de 2021 .

[…] La Junta de Planificación […] Este seminario ha sido desarrollado a través de una extensa investigación de campo por el Instituto de Desarrollo Profesional en consulta con la Junta de Asesores Técnicos de los Institutos RCA, que representa varias actividades de investigación técnica y educativas de RCA y sus subsidiarias. […] BI Daggett (Director), JH Sneddon (Gerente, Administración), DB Kenney (Ventas industriales), BV Ferguson (Marketing directo), MV Mahoney (Investigación y desarrollo), AB Peticolas (Administrador), JB Wetterau (Líder de grupo ), E. Fleisher (miembro del personal), MC Laguzzi (miembro del personal), RD Lindskog (miembro del personal), CL Pearce (miembro del personal), P. Pennisi (miembro del personal), CH Saville (miembro del personal), REWeiss (miembro del personal) […] Tabla de contenido […] El enfoque matricial de la notación numérica de designación lógica […] Números de designación de elementos y funciones booleanos, operaciones lógicas con números de designación […] El mapa lógico […] Desarrollo del Mapa de Mahoney […]

[13] (NB. Este volante de 1968 menciona a Mahoney como miembro de I + D de RCA . Los miembros del curso disponían de una carpeta de notas de clase de 184 páginas ). - ^ "Diseño lógico: desarrollo del mapa de Mahoney". Escrito en Montreal, Quebec, Canadá. RCA - Un curso en diseño lógico - Una experiencia de aprendizaje única para aquellos que resuelven problemas de diseño de circuitos digitales o que evalúan la efectividad del diseño lógico - Un seminario preparado por el Instituto de Desarrollo Profesional de los Institutos RCA . Lecture Notes Manual (carpeta del estudiante) (folleto). Clark, Nueva Jersey, EE. UU .: RCA Institutes, Inc. 1970-08-24. pag. 2.5. arca: / 13960 / t7jq7zk56 . Consultado el 16 de febrero de 2021 . pag. 2.5:

[…] Cursos de RCA para Desarrollo Profesional, desde que nuestros programas se formaron por primera vez en 1964. […] Diseño lógico […] La técnica de reducción que se explorará a continuación y se utilizará de ahora en adelante en nuestro trabajo de diseño lógico es una variación del diagrama de Veitch . Esta modificación, introducida por M. V. Mahoney, está diseñada para funcionar directamente desde los números de designación; el diseñador nunca necesita ver una expresión booleana que no sea la forma simplificada final. Con este mapa en particular, la posición de cada minitérminoes invariante, independientemente del número de variables, por lo que el patrón del mapa se memoriza fácilmente. […] Definiciones y conceptos básicos […] Sea f = cualquier función […] #f = el número de designación de f (lea "designación f") […] n = número de variables (f es una función de n variables) […] P = número de posiciones en #f […] p = número de subconjuntos cuadrados en el universo […] i = identificación de posición […] m i = el minitérmino que ocupa la posición i […] Primero asumiremos que n = 0. Como en el diagrama de Venn original , el universo será un rectángulo. Con n = 0, no podemos subdividir este conjunto universal. Sin embargo, no es necesario, porque si n = 0, p = 2 0 = 1. En otras palabras, solo hay una posición en #f, el ceroposición, y solo un minitérmino posible, m 0 . El universo rectangular representará m 0 y estará marcado con el subíndice de minitérmino: […] n = 0 [o] No. de subconjuntos (cuadrados) = no. de posiciones mínimas = p = 2 n = 2 0 = 1 […] Aunque no hay variables, todavía hay 2 p = 2 funciones posibles. Estas funciones deben ser las dos constantes, 1 y 0. […] Si f = 0, entonces #f = 0; es decir, m 0 está vacío . Esto se indica dejando el diagrama sin marcar: [o] #f = 0; f = 0; p = 2 n = 1 […] Si f = 1, entonces #f = 1; es decir, el m 0la posición está ocupada. Esto se indica con una marca diagonal: [/ o /] #f = 1; f = 1; f = m 0 […] El mapa anterior, por supuesto, nunca sería necesario en un problema práctico. Aquí se usa solo como una introducción, para la evolución ordenada del mapa general de n variables. […] Desarrollo del mapa […] Visualice el mapa como una hoja grande marcada con un patrón de cuadros de tablero de ajedrez. Ahora dobla la mitad inferior hacia arriba para que quede oculta detrás de la parte superior. Doble la mitad de la mano derecha detrás de la izquierda. Repita los procedimientos anteriores alternativamente, hasta que solo quede visible el cuadrado superior izquierdo. Este cuadrado es el conjunto que representa el mínimo de cero, el cuadrado que se utiliza como punto de partida. […]

[14] (NB. Este volante de 1970 menciona que el curso se estableció en 1964.) - ^ Fezer, Harold (diciembre de 1970 - enero de 1971). "La evolución y desarrollo de los Institutos RCA" (PDF) . Ingeniero RCA . Nueva Jersey, EE.UU .: RCA Corporate Engineering Services / RCA Corporation . 16 (4): 64–69 [67]. Archivado (PDF) desde el original el 19 de febrero de 2021 . Consultado el 19 de febrero de 2021 . pag. 67:

Diseño lógico (5 días): proporciona las herramientas numéricas y matriciales necesarias para seleccionar el enfoque más sencillo y práctico para el diseño de circuitos digitales.

El mapa de Mahoney y los números de designación están completamente cubiertos.

[15] - ^ Moser, Jr., Carl Woodrow (19 de julio de 1973) [enero de 1973]. Escrito en Western Electric, Winston-Salem, Carolina del Norte, EE. UU. "Comprobación de puertas Y cableadas en una sola configuración de prueba" . Cuaderno del ingeniero. Electronics - La revista internacional de tecnología electrónica . Vol. 46 no. 15. Nueva York, Estados Unidos: McGraw-Hill, Inc. p. 127. ISSN 0013-5070 . Archivado desde el original el 16 de febrero de 2021 . Consultado el 16 de febrero de 2021 . pag. 127:

[…] Uno de los tipos de circuitos más difíciles de probar de manera efectiva es una matriz de puertas lógicas Y cableadas. Pero se puede utilizar una ayuda de diseño estándar, el mapa de Mahoney, para determinar la mejor configuración de forma de onda para probar por completo dicha matriz. El mapa de Mahoney es idéntico al mapa de Karnaugh , con la excepción de los dígitos del minitérmino . […]

[16] [17] (1 página) - ↑ van Holten, Cornelis "Cornelius" (agosto de 1974). Escrito en la Universidad Técnica de Delft, Delft, Países Bajos. "Capacidad lógica de doble multiplexor: mediante el uso de una de las variables de entrada para controlar algunas líneas de datos. Un mapa de Karnaugh modificado le ayuda a elegir las correctas" . Diseño electrónico : para ingenieros y gerentes de ingeniería . Vol. 22 no. 17. Rochelle Park, Nueva Jersey, Estados Unidos: Hayden Publishing Company, Inc. págs. 86-89 [87, 89]. ISSN 0013-4872 . Consultado el 20 de febrero de 2021 . (4 páginas)

- ↑ Krehbiel, Paul (5 de diciembre de 1996). Bonal, David (ed.). (Comunicación privada) .(NB. Citado en Bonal . [18] )

- ↑ Mann, Kenneth (18 de diciembre de 2005) [19 de noviembre de 2005]. "Tutorial de mapas de Karnaugh" . PhysicsForums . Archivado desde el original el 16 de febrero de 2021 . Consultado el 16 de febrero de 2021 .

[…] Aproximadamente una década después

del artículo de Karnaugh

, un individuo llamado Matthew Mahoney observó un enfoque reflectante simétrico detrás del proceso de construcción de mapas que mostraba que los mapas podían extenderse en diseño más allá de cuatro variables, y a partir de ese enfoque se le ocurrió un diseño ligeramente diferente que se denominó 'Mapa Mahoney'. '. […] A principios de la década de 1960, Matthew Mahoney definió con mayor precisión el mecanismo básico a través del cual opera el mapa lógico. Utilizando este principio (que ya hemos expuesto), definió y trazó lo que llegó a llamarse el "Mapa de Mahoney". Básicamente, el mapa de Mahoney es una variación del mapa de Karnaugh y los principios se aplicarán por igual en ambos casos. […]

[19] [20] - ↑ Goth, Andrew "Andy" Michael (27 de noviembre de 2012) [28 de enero de 2009]. "Mapa de Mahoney: una alternativa a los mapas de Karnaugh" . Midlothian, Texas, Estados Unidos. Archivado desde el original el 16 de febrero de 2021 . Consultado el 16 de febrero de 2021 .

- ↑ Bonal, David (19 de octubre de 2013). "Karnaugh y Mahoney: métodos de mapa para minimizar las expresiones booleanas" . Sección 3. Mapas de Mahoney: Implementando el Signo de Zoro. Archivado desde el original el 16 de febrero de 2021 . Consultado el 16 de febrero de 2021 .

- ^ Kortum, Herbert Franz (1965). "Minimierung von Kontaktschaltungen durch Kombination von Kürzungsverfahren und Graphenmethoden" [Minimización de circuitos de contacto mediante la combinación de procedimientos de reducción y métodos gráficos]. messen-steuern-regeln (msr) (en alemán). Berlín / Leipzig, Alemania: VEB Verlag Technik . 8 (12): 421–425. ISSN 0026-0347 . OCLC 310970250 . CODEN MSRGAN , MSRGA , MMSRD . DNB-IDN 01269357X . ZDB-ID 512087-1 . Consultado el 4 de noviembre de 2020 . (5 páginas)

- ^ Kortum, Herbert Franz (1966). "Konstruktion und Minimierung von Halbleiterschaltnetzwerken mittels Graphentransformation" . messen-steuern-regeln (msr) (en alemán). Berlín / Leipzig, Alemania: VEB Verlag Technik . 9 (1): 9-12. ISSN 0026-0347 . OCLC 310970250 . CODEN MSRGAN , MSRGA , MMSRD . DNB-IDN 01269357X . ZDB-ID 512087-1 . Consultado el 17 de junio de 2018 .

- ^ Kortum, Herbert Franz (1966). "Weitere Bemerkungen zur Minimierung von Schaltnetzwerken mittels Graphenmethoden" . messen-steuern-regeln (msr) (en alemán). Berlín / Leipzig, Alemania: VEB Verlag Technik . 9 (3): 96–102. ISSN 0026-0347 . OCLC 310970250 . CODEN MSRGAN , MSRGA , MMSRD . DNB-IDN 01269357X . ZDB-ID 512087-1 . Consultado el 17 de junio de 2018 .

- ^ Kortum, Herbert Franz (1965). "Weitere Bemerkungen zur Behandlung von Schaltnetzwerken mittels Graphen" [Otras observaciones sobre el tratamiento de las redes de conmutación mediante gráficos]. Regelungstechnik (documento de conferencia). 10. Internationales Wissenschaftliches Kolloquium. [10º coloquio científico internacional] (en alemán). Technische Hochschule Ilmenau . 10 (5): 33–39 . Consultado el 4 de noviembre de 2020. (7 páginas); Kortum, Herbert Franz (1966). "Weitere Bemerkungen zur Behandlung von Schaltnetzwerken mittels Graphen. Konstruktion von vermaschten Netzwerken (Brückenschaltungen)" [Otras observaciones sobre el tratamiento de las redes de conmutación mediante gráficos]. messen-steuern-regeln (msr) (en alemán). Berlín / Leipzig, Alemania: VEB Verlag Technik . 9 (5): 151-157. ISSN 0026-0347 . OCLC 310970250 . CODEN MSRGAN , MSRGA , MMSRD . DNB-IDN 01269357X . ZDB-ID 512087-1 .

- ^ Kortum, Herbert Franz (1967). "Über zweckmäßige Anpassung der Graphenstruktur diskreter Systeme an vorgegebene Aufgabenstellungen". messen-steuern-regeln (msr) (en alemán). Berlín / Leipzig, Alemania: VEB Verlag Technik . 10 (6): 208–211. ISSN 0026-0347 . OCLC 310970250 . CODEN MSRGAN , MSRGA , MMSRD . DNB-IDN 01269357X . ZDB-ID 512087-1 .

- ^ Kortum, Herbert Franz (1966) [1965]. "Zur Minimierung von Schaltsystemen" [Minimización de circuitos de conmutación]. Wissenschaftliche Zeitschrift der TU Ilmenau (en alemán). Jena, Alemania: Technische Hochschule für Elektrotechnik Ilmenau / Forschungsstelle für Meßtechnik und Automatisierung der Deutschen Akademie der Wissenschaften. 12 (2): 181–186 . Consultado el 4 de noviembre de 2020 . (6 páginas)

- ^ Tafel, Hans Jörg (1971). "4.3.5. Graphenmethode zur Vereinfachung von Schaltfunktionen". Escrito en RWTH , Aachen, Alemania. Einführung in die digitale Datenverarbeitung [ Introducción al procesamiento de información digital ] (en alemán). Munich, Alemania: Carl Hanser Verlag . págs. 98-105, 107-113. ISBN 3-446-10569-7.

- ↑ Axmann, Hans-Peter (2019) [13 de junio de 1979]. Einführung in die technische Informatik: Funktionsweise digitaler Bausteine und deren Verwendung in Datenerfassungssystemen (en alemán) (reimpresión de la 1ª ed.). Springer-Verlag Wien GmbH . pag. 37. doi : 10.1007 / 978-3-7091-4478-7 . ISBN 978-3-211-81546-5. Consultado el 15 de abril de 2020 . pag. 37:

[…] Die Graphenmethode zur Vereinfachung von Schaltfunktionen zeichnet sich durch besondere Anschaulichkeit und Einfachheit aus. Sie ist dann besonders vorteilhaft, wenn die Schaltfunktion unter Verwendung bestimmter Verknüpfungsglieder mit minimalem Aufwand an Bauelementen und Verbindungsleitungen zu realisieren ist. Sie ist anderen Methoden, besonders bei der Netzwerksynthese von Brückenschaltungen wie auch bei der Optimierung von Kontaktschaltungen mit Sperrdioden, überlegen. Die erfolgreiche Anwendung der Graphenmethode setzt voraus, daß die vorgegebene Funktion bereits in einer weitgehend vereinfachten Form vorliegt, da mit dieser Methode Redundanzen nur noch sehr schwer zu eliminieren sind. […]

(290 páginas) - ↑ Winkler, Jürgen FH (7 de abril de 2013) [25 de octubre de 2008]. "Die Oprema - der Relaisrechner des Zeisswerks Jena" (PDF) (Notas de la conferencia) (en alemán). Universidad Friedrich Schiller , Jena, Alemania. págs. 1–27. Archivado desde el original (PDF) el 30 de agosto de 2017. (27 páginas)

- ↑ Winkler, Jürgen FH (26 de agosto de 2019) [25 de octubre de 2014]. "Oprema - La computadora de retransmisión de Carl Zeiss Jena" (PDF) . 1. Universidad Friedrich Schiller , Jena, Alemania. págs. 1-33. arXiv : 1908.09549 . Archivado (PDF) desde el original el 29 de septiembre de 2020 . Consultado el 4 de noviembre de 2020 . (33 páginas)

- ↑ a b Burgoon, J. Robert "Rob" (21 de diciembre de 1972). Escrito en Hewlett-Packard, División de Santa Clara, Santa Clara, California, EE. UU. "Mejore sus habilidades de mapeo de Karnaugh. El uso de variables le permite simplificar mapas y diseñar circuitos para enclavamiento o compuerta de señal secuencial" (PDF) . Diseño electrónico : para ingenieros y gerentes de ingeniería . Vol. 20 no. 26. Rochelle Park, Nueva Jersey, Estados Unidos: Hayden Publishing Company, Inc. págs. 54–56. ISSN 0013-4872 . Archivado (PDF) desde el original el 14 de febrero de 2021 . Consultado el 14 de febrero de 2021 . (3 páginas) (NB. En Muroga se analiza una ligera extensión de este método por Larry L. Dornhoff .)

- ↑ a b Vingron, Shimon Peter (2004) [5 de noviembre de 2003]. "Capítulo 20. Mapas de Karnaugh reducidos". Switching Theory: Insight Through Predicate Logic (1 ed.). Berlín, Heidelberg, Nueva York: Springer-Verlag . págs. 207–217. doi : 10.1007 / 978-3-662-10174-2 . ISBN 3-540-40343-4.

- ↑ a b Vingron, Shimon Peter (2012). "5.5 Árboles de Karnaugh y variables introducidas en el mapa". Escrito en Hinterbrühl, Austria. Diseño de circuitos lógicos: métodos seleccionados (1 ed.). Berlín y Heidelberg, Alemania: Springer-Verlag . págs. 63–66. doi : 10.1007 / 978-3-642-27657-6 . ISBN 978-3-642-43256-9. (xiv + 258 páginas)

- ^ Schultz, GW (marzo de 1969). Escrito en Central Data Systems, Inc., Sunnyvale, California, EE. UU. "Un algoritmo para la síntesis de redes secuenciales complejas" . Diseño informático . Vol. 8 no. 3. Concord, Massachusetts, Estados Unidos: Computer Design Publishing Corporation. págs. 49–55. ISSN 0010-4566 . OCLC 828863003 . CODEN CMPDA . Consultado el 22 de febrero de 2021 . (7 páginas) (NB. Este artículo provocó una serie de cartas al editor en números posteriores de la revista).

- ^ a b Schultz, GW (1969). Escrito en Central Data Systems, Inc., Sunnyvale, California, EE. UU. "Para el editor" . Cartas al editor. Diseño informático . Vol. 8 no. 5–12 ?. Concord, Massachusetts, Estados Unidos: Computer Design Publishing Corporation. pag. 10. ISSN 0010-4566 . OCLC 828863003 . CODEN CMPDA . pag. 10:

[…] En su número de abril, publicó una

carta de RL Dineley que

describe un método simple para tratar

expresiones lógicas

producto de sumas

. […]

DA Huffman

enseña un método aún más simple

. Este método se basa en reconocer que la

expresión booleana

será cero cuando cualquiera de los factores en la forma del producto de sumas sea cero. Trazar ceros de factores en un diagrama de Veitch o mapa de Karnaugh es tan fácil como ubicar unos para una expresión de suma de productos . […] Para ilustrar, usando el ejemplo de Dineley (A + BC) (A + C): […] Los ceros resultantes de A + BC estarán ubicados donde tanto A como BC sean cero. Por tanto, ubicamos en el mapa la expresión A * BC (que es igual a A * B + A * C ). De manera similar, los ceros de A + C se ubican y se grafican en A * C. Con todos los ceros ubicados, el resto del mapa puede llenarse con unos. Uno puede ser un poco más formal y calcular algebraicamente el complemento lógico de la expresión en consideración y luego graficar ceros para esa expresión resultante. Sin embargo, en una representación simple de producto de sumas, los términos complementarios pueden escribirse mediante inspección; o los ceros pueden trazarse por inspección sin escribir la expresión completa […] "Reducción clásica que involucra variables de uso poco frecuente" 11 de octubre de 1968. Universidad de Santa Clara […] El trabajo del Sr. Osborne se parece mucho al que presenté en Este artículoy por tanto, sin duda sería de interés para aquellos lectores que busquen más información. Tengo entendido que ha trabajado para aplicar la técnica de variables infrecuentes al diseño de redes secuenciales construidas a partir de memoria de solo lectura . Dado que aún no ha publicado nada sobre esta área, si los lectores desean información adicional, pueden escribir al Sr. Osborne a: […] Thomas E. Osborne […] Edificio 1U […] 1501 Page Mill Road […] Palo Alto , California […] Gracias por la oportunidad de publicar contigo. […] GW Schultz […] Central Data Systems, Inc. […] Sunnyvale, Calif.

(1 página) (NB. El método de Osborne fue publicado más tarde por Clare. [B] ) - ^ Langdon, Jr., Glen G. (1974). "Capítulo 4. Interrelaciones, D. Diseño lógico y teoría de la conmutación, 3. La tabla de flujo como punto de partida para el diseño". Escrito en IBM Corporation, San José, California, EE. UU. En Ashenhurst, Robert "Bob" Lovett (ed.). Diseño lógico: una revisión de la teoría y la práctica . Serie de monografías ACM (1 ed.). Nueva York, Estados Unidos: Academic Press, Inc. - Subsidiaria de Harcourt Brace Jovanovich, Publishers . pag. 149. ISBN 0-12-436550-7. ISSN 0572-4252 . LCCN 73-18988 . ISBN 978-0-12-436550-6 . Archivado desde el original el 17 de abril de 2021 . Consultado el 17 de abril de 2021 . pag. 149:

[…] Schultz hizo una importante contribución a la adaptación de la teoría a la práctica

[20].

; se basa en la comprensión básica del problema por parte del diseñador y le pide que identifique las "variables poco frecuentes". Definidas libremente, estas variables no se relacionan con todos los estados internos, es decir, no son necesarias para definir todos los estados. En esencia, las variables poco frecuentes son relevantes solo para unos pocos (quizás uno o dos) estados o transiciones de estados. Schultz sugiere que el diseñador primero traduzca el problema verbal a un gráfico de transición de estado que se reduce. Los estados internos se codifican y luego se agrega información sobre variables poco frecuentes a las transiciones de estado apropiadas. Se hace una "primera aproximación" a las ecuaciones de entrada flip-flop, basada sólo en las variables frecuentes.Schultz demuestra cómo estas ecuaciones pueden modificarse posteriormente para incorporar transiciones controladas por las variables poco frecuentes. En los ejemplos de Schultz, las variables poco frecuentes son todas señales de entrada, pero esta idea también se aplica a las señales de variables de estado internas que pueden considerarse "poco frecuentes". En este caso, por ejemplo, un flip-flop de variable de estado interno poco frecuente podría establecerse por una circunstancia particular y restablecerse en algún momento posterior. La salida del flip-flop ahora puede tratarse como una variable de entrada poco frecuente. […]un flip-flop de variable de estado interno infrecuente puede establecerse por una circunstancia particular y restablecerse en algún momento posterior. La salida del flip-flop ahora puede tratarse como una variable de entrada poco frecuente. […]un flip-flop de variable de estado interno infrecuente puede establecerse por una circunstancia particular y restablecerse en algún momento posterior. La salida del flip-flop ahora puede tratarse como una variable de entrada poco frecuente. […]

(ix + 1 + 179 + 3 páginas) - ^ Clare, Christopher "Chris" R. (febrero de 1971) [noviembre de 1970]. Diseño lógico de máquinas de estados algorítmicos . Laboratorios Hewlett-Packard, EE.UU .: Hewlett-Packard . Número de catálogo de CHM 102650285.(110 páginas) [21] (NB. Varias revisiones internas existieron en 1970 y 1971. Esto fue publicado más tarde por McGraw-Hill. [A] El método de simplificación de Thomas E. Osborne ya fue mencionado por GW Schultz en 1969.)

- ^ Clare, Christopher "Chris" R. (1973) [noviembre de 1972]. "Reducir el tamaño del mapa necesario con variables introducidas en el mapa". Diseño de sistemas lógicos mediante máquinas de estados (PDF) . Osborne, Thomas "Tom" E. (contribuciones iniciales) (1 ed.). Laboratorio de investigación electrónica, Laboratorios Hewlett-Packard: McGraw-Hill, Inc. págs. 41–42. ISBN 0-07011120-0. S2CID 60509061 . SBN 07-011120-0. ISBN 978-0-07011120-2 . arca: / 13960 / t9383kw8n. 79876543 . Consultado el 14 de febrero de 2021 . (2 páginas de vii + 114 + 3 páginas) [22] (NB. Este libro está basado en un documento interno de Hewlett-Packard de 1970. [B] Una ligera extensión de este método por Larry L. Dornhoff se analiza en Muroga .)

- ↑ a b Muroga, Saburo (1979). Diseño lógico y teoría de la conmutación (1 ed.). Nueva York, Estados Unidos: John Wiley and Sons, Inc. págs. 161–163. ISBN 0-47104418-0. ISBN 978-0-47104418-5 . (3 páginas de 617 páginas); Muroga, Saburo (enero de 1990) [1979]. Diseño lógico y teoría de la conmutación (reimpresión actualizada ed.). Malabar, Florida, EE.UU .: Robert E. Krieger Publishing Company, Inc. págs. 161–163. ISBN 0-89464-463-7. LCCN 90-32076 .(617 + 5-6 + 32 páginas) (NB. Los capítulos originales 6.3–6.6 (páginas 281–320) fueron reemplazados por nuevos capítulos 6.3–6.5 (páginas insertadas 1–32); también en 1997 con ISBN 1-57524036-X , 978-1-57524036-7 . El método descrito aquí es una pequeña extensión por Larry L. Dornhoff del método discutido en Burgoon y Clare . Una extensión adicional de este método es descrita por Rushdi .)

- ↑ a b Fletcher, William "Bill" Isaac (1980) [1979]. Escrito en Logan, Utah, EE. UU. Un enfoque de ingeniería para el diseño digital (1 ed.). Englewood-Cliffs, Nueva Jersey, EE.UU .: Prentice Hall, Inc. págs. 157–166. ISBN 0-13-277699-5. LCCN 78-27177 . S2CID 38105765 . ISBN 978-0-13-2776998 . (xviii + 766 páginas) (NB. El método descrito aquí se aplica a las funciones de conmutación generales que pueden especificarse de forma incompleta con respecto al mapa y las variables ingresadas, pero se limita a los casos en los que solo una sola variable o productos de un solo literal que involucran pocos Las variables de uso poco frecuente se ingresan en el mapa. Se trata como un caso especial en Rushdi 1987 ).

- ^ Mano, M. Morris; Ciletti, Michael D. Diseño digital . págs. 112-119.

- ^ Verde, David H. (1986). Diseño de lógica moderna . Serie de Ingeniería de Sistemas Electrónicos (1ª edición ilustrada). Wokingham, Reino Unido: Addison-Wesley Publishing Company, Inc. ISBN 0-201-14541-3. LCCN 85-20063 . ISBN 978-0-201-145410 . (x + 269 + 1 páginas)

- ↑ Green, David H. (21 de junio de 1993) [19 de mayo de 1993]. "Simplificación de las funciones de conmutación mediante mapas de introducción de variables" . Revista Internacional de Electrónica . Técnicas y análisis de circuitos. Taylor y Francis . 75 (5): 877–886. doi : 10.1080 / 00207219308907166 . Consultado el 18 de febrero de 2021 .

- ↑ a b McCalla, Thomas Richard (1992). "3.5 Minterm-Ring Maps y Karnaugh Maps en 5 y 6 variables". Escrito en la Universidad de Ciencias y Artes de Oklahoma, Chickasha, Oklahoma, EE. UU. Lógica digital y diseño informático . Serie internacional de Merrill en tecnología de ingeniería (1 ed.). Englewood Cliffs, Nueva Jersey, EE.UU .: Macmillan Publishing . págs. 119-135, 201-203 [119, 122, 123, 125-128, 130-132, 135]. ISBN 0-675-21170-0. LCCN 91-17012 . ISBN 978-0-675-21170-3 . Consultado el 20 de febrero de 2021 . (xx + 790 + 6 páginas)

- ↑ a b Misra, Krishna B. (1 de junio de 1992). "2.2.12 Variable ingresada en el mapa de Karnaugh" . Análisis y predicción de confiabilidad: un tratamiento orientado a la metodología . Estudios Fundamentales en Ingeniería. Elsevier Science Ltd . págs. 56–62. ISBN 0-44489606-6. ISBN 978-0-44489606-3 . Consultado el 18 de febrero de 2021 . (906 páginas)

- ↑ Rushdi, Ali Muhammad Ali (julio de 1983) [14 de enero de 1983, 16 de abril de 1982]. "Análisis de confiabilidad simbólica con la ayuda de mapas de Karnaugh ingresados de forma variable" . Transacciones IEEE sobre confiabilidad . Universidad King Abdul Aziz, Jeddah, Arabia Saudita: IEEE . R-32 (2): 134-139. doi : 10.1109 / TR.1983.5221510 . eISSN 1558-1721 . ISSN 0018-9529 . Manuscrito TR82-38. Archivado desde el original el 14 de febrero de 2021 . Consultado el 14 de febrero de 2021 . [23]

- ^ Rushdi, Ali Muhammad Ali (enero de 1985) [diciembre de 1984]. "Sobre la evaluación de la confiabilidad por descomposición de la red" . Transacciones IEEE sobre confiabilidad . Universidad King Abdul Aziz, Jeddah, Arabia Saudita: IEEE . R-33 (5): 379–384. doi : 10.1109 / TR.1984.5221873 . eISSN 1558-1721 . ISSN 0018-9529 . Archivado desde el original el 18 de febrero de 2021 . Consultado el 18 de febrero de 2021 . [24]

- ^ Rushdi, Ali Muhammad Ali (1985). "Derivación del mapa de la suma mínima de una función de conmutación de la de su complemento" . Fiabilidad de la microelectrónica . Universidad King Abdul Aziz, Jeddah, Arabia Saudita. 25 (6): 1055–1065. doi : 10.1016 / 0026-2714 (85) 90481-0 . ISSN 0026-2714 . S2CID 120166912 . Archivado desde el original el 17 de febrero de 2021 . Consultado el 17 de febrero de 2021 . (NB. Este método es una extensión del método descrito en Muroga que permite la subsunción general y las relaciones de consenso entre los productos ingresados, pero no maneja funciones especificadas de manera incompleta con respecto a las variables ingresadas. Se mejoró aún más en 1987 ).

- ↑ Rushdi, Ali Muhammad Ali (1986) [8 de abril de 1986]. "Mapa de diferenciación de funciones de conmutación" . Fiabilidad de la microelectrónica . Universidad King Abdul Aziz, Jeddah, Arabia Saudita. 26 (5): 891–907. doi : 10.1016 / 0026-2714 (86) 90233-7 . ISSN 0026-2714 . Consultado el 18 de febrero de 2021 .

- ↑ Rushdi, Ali Muhammad Ali (diciembre de 1987) [1 de junio de 1986]. "Procedimientos mejorados del mapa de Karnaugh introducido por variables" . Computación e Ingeniería Eléctrica . Universidad King Abdul Aziz, Jeddah, Arabia Saudita: Pergamon Journals Ltd. 13 (1): 41–52. doi : 10.1016 / 0045-7906 (87) 90021-8 . ISSN 0045-7906 . OCLC 38840818 . Archivado desde el original el 17 de febrero de 2021 . Consultado el 15 de febrero de 2021 . [25] (NB. Una variante mejorada del método descrito en 1985 , cubre el método de Fletcher como un caso especial).

- ↑ Koo, David Y. (1990) [25 de enero de 1990]. "Aplicación D / Boolean en Análisis de Confiabilidad" . Simposio de Actas Anuales sobre Confiabilidad y Mantenibilidad : 295–302. doi : 10.1109 / ARMS.1990.67972 . S2CID 123353547 . Consultado el 18 de febrero de 2021 .

- ↑ a b Romero-Aguirre, Eduardo; Murrieta-Lee, Juan Carlos (2 de marzo de 2005) [28 de febrero de 2005]. "Un estudio del método alternativo gráfico para la simplificación de funciones booleanas" . Actas de la XV Conferencia Internacional de Electrónica, Comunicaciones y Computación (CONIELECOMP 2005) . Educación. Instituto Tecnológico de Sonora (ITSON), Puebla, México: IEEE Computer Society . 1 : 328–334. doi : 10.1109 / CONIEL.2005.12 . ISBN 0-7695-2283-1. Archivado desde el original el 15 de febrero de 2021 . Consultado el 17 de febrero de 2021 . [26] [27] [28]

- ↑ Malhotra, Mohit (25 de noviembre de 2019). "Mapa de entrada variable (VEM) en lógica digital" . Geeks para geeks . Archivado desde el original el 14 de febrero de 2021 . Consultado el 14 de febrero de 2021 .

- ↑ Kartalopoulos, Stamatios V. (18 de febrero de 1982) [28 de enero de 1982]. "La minimización de funciones lógicas utilizando representaciones bidimensionales de hipercubos" . Revista Internacional de Electrónica . Taylor y Francis . 53 (3): 233–245. doi : 10.1080 / 00207218208901505 . Consultado el 31 de enero de 2021 .

- ↑ McCalla, Thomas Richard (1991) [14 de agosto de 1990]. "Un algoritmo de anillo mínimo para simplificar expresiones booleanas" . En Johnston, Ronald H .; Nowrouzian, Behrooz; Turner, Laurence E. (eds.). Actas del 33 ° Simposio del Medio Oeste sobre Circuitos y Sistemas (MWSCAS): 12 al 15 de agosto de 1990, Centro de Convenciones de Calgary, Calgary, Alberta, Canadá . II . Centro de Convenciones de Calgary, Calgary, Alberta, Canadá: IEEE / Departamento de Ingeniería Eléctrica, Universidad de Calgary y Universidad de Alberta. págs. 1127-1130. doi : 10.1109 / MWSCAS.1990.140924 . ISBN 0-7803-0081-5. Gato. No. 90CH2819-1 . Consultado el 15 de febrero de 2021 . [29]

- ^ Morelli Reynaga, Jorge Alberto (enero de 2004). Métodos Gráficos Alternos para Simplificación de Funciones Booleanas de 5 y 6 Variables (Tesis). Sonora, México: Instituto Tecnológico de Sonora (ITSON).

- ↑ Westphal, Jonathan (7 de agosto de 2007) [5 de octubre de 2001, 6 de octubre de 2000]. "Dispositivos y técnicas de procesamiento lógico" (PDF) . Patente US7254304B2. Archivado (PDF) desde el original el 9 de mayo de 2020 . Consultado el 9 de mayo de 2020 . [30] (77 páginas)

- ^ Westphal, Jonathan ; Hardy, Jim (1 de octubre de 2005) [16 de febrero de 2004]. "Lógica como sistema vectorial" . Revista de Lógica y Computación . Universidad Estatal de Idaho , Pocatello, Idaho, EE.UU .: Oxford University Press . 15 (5): 751–765. doi : 10.1093 / logcom / exi040 . Archivado desde el original el 9 de mayo de 2020 . Consultado el 9 de mayo de 2020 . [31] (15 páginas)

- ^ Verma, Shrish; Permar, Kiran D. Escrito en Government Engineering College, Raipur, India. "Un método novedoso para minimizar las funciones booleanas utilizando código Gray y desarrollo de un algoritmo paralelo" (PDF) . VI Taller Internacional sobre Problemas Booleanos, 24-09-2004 . Freiberg, Alemania. Archivado (PDF) desde el original el 8 de noviembre de 2007 . Consultado el 31 de enero de 2021 . [32] (24 páginas)

- ^ Verma, Shrish. Permar, Kiran D. (ed.). Paraboomig: un método novedoso para minimizar las funciones booleanas utilizando código Gray y su algoritmo paralelo (tesis). Instituto Nacional de Tecnología, Raipur, India. hdl : 10603/30623 . Archivado desde el original el 31 de enero de 2021 . Consultado el 31 de enero de 2021 . [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47]

- ^ Amarú, Luca; Gaillardon, Pierre-Emmanuel; De Micheli, Giovanni (5 de mayo de 2014) [1 de mayo de 2014]. Escrito en Suiza. "Gráfico de inversor mayoritario: una estructura de datos y algoritmos novedosos para una optimización lógica eficiente" . Actas de la 51ª Conferencia Anual de Automatización del Diseño (DAC) . San Francisco, California, Estados Unidos: Asociación de Maquinaria de Computación (ACM): 1–6. doi : 10.1145 / 2593069.2593158 . Archivado desde el original el 9 de mayo de 2020 . Consultado el 9 de mayo de 2020 . (6 páginas)

- ^ Amarú, Luca; Gaillardon, Pierre-Emmanuel; De Micheli, Giovanni (2016). Escrito en Suiza. "Gráfico de inversor mayoritario: una estructura de datos y algoritmos novedosos para una optimización lógica eficiente" . Transacciones IEEE sobre diseño asistido por computadora de circuitos y sistemas integrados . San Francisco, California, Estados Unidos: IEEE . 35 (5): 806–819. doi : 10.1145 / 2593069.2593158 . ISBN 978-1-4799-3017-3. ISSN 0738-100X . Consultado el 9 de mayo de 2020 . (14 páginas)

- ^ Pandit, Vedhas; Schuller, Björn Wolfgang (31 de diciembre de 2017) [14 de noviembre de 2017, 11 de octubre de 2017, 5 de mayo de 2017]. Scarpiniti, Michele (ed.). "Una técnica gráfica novedosa para la representación y optimización de la lógica combinacional" (PDF) . Complejidad . Hindawi Publishing Corporation / John Wiley & Sons, Inc. 2017 (5): 1–12. doi : 10.1155 / 2017/9696342 . eISSN 1099-0526 . ISSN 1076-2787 . ID de artículo 9696342. Archivado (PDF) desde el original el 9 de mayo de 2020 . Consultado el 9 de mayo de 2020 . (12 páginas)

- ↑ Alharbi, Eisa (17 de agosto de 2020). "Gráfico de verdad: un método novedoso para minimizar las expresiones del álgebra booleana mediante el uso de gráficos" (PDF) . En Pietarinen, Ahti-Veikko; Chapman, Peter; Bosveld-de Smet, Leonie; Giardino, Valeria; Corter, James; Linker, Sven (eds.). Representación e inferencia esquemática . Actas de la 11ª Conferencia Internacional sobre Teoría y Aplicación de Diagramas "Diagramas 2020", Tallin, Estonia, 2020-08-24 / 28 (documento de conferencia). Lecture Notes in Computer Science (LNCS) / Lecture Notes in Artificial Intelligence (LNAI). 12169 . Ahmadi, Kuwait: Springer Science + Business Media . págs. 461–469. doi : 10.1007 / 978-3-030-54249-8_36 . ISBN 978-3-030-54248-1. Archivado (PDF) desde el original el 8 de noviembre de 2020 . Consultado el 8 de noviembre de 2020 . [48] (9 páginas)

- ↑ Alharbi, Eisa (24 de agosto de 2020) [15 de junio de 2020]. Expresiones del gráfico de verdad: método de minimización del gráfico de verdad (vídeo) . Consultado el 14 de febrero de 2021 .

Lectura adicional

- Hwa, "Sherman" Hsuen Ren (junio de 1974). "Un método de generación de los principales implicantes de una expresión booleana" . Transacciones IEEE en computadoras . IEEE . C-23 (6): 637–641. doi : 10.1109 / TC.1974.224003 . eISSN 1557-9956 . ISSN 0018-9340 . S2CID 10646917 . CD- ISSN 2326-3814 . 1F09 . Consultado el 12 de mayo de 2020 ; Hwa, "Sherman" Hsuen Ren (abril de 1973). Un método para generar implicantes primos de una expresión booleana . Departamento de Ciencias de la Computación de Basser, Universidad de Sydney . Informe técnico 82.

- Lind, Larry Frederick; Nelson, John Christopher Cunliffe (1977). Análisis y Diseño de Sistemas Digitales Secuenciales . Prensa Macmillan . ISBN 0-33319266-4. [49] (146 páginas)

- Ghosh, Debidas (junio de 1977) [21 de enero de 1977]. "Un método de generación de factores primos de una expresión booleana en una forma normal conjuntiva con la posibilidad de inclusión de la combinación No importa" (PDF) . Revista de tecnología . Departamento de Matemáticas, Facultad de Ingeniería de Bengala, Howrah, India. XXII (1). Archivado (PDF) desde el original el 12 de mayo de 2020 . Consultado el 12 de mayo de 2020 .

- De Micheli, Giovanni (1994). Síntesis y Optimización de Circuitos Digitales . McGraw-Hill . ISBN 0-07-016333-2. (NB. Los capítulos 7 a 9 cubren la optimización combinatoria de dos niveles, combinatoria multinivel y, respectivamente, la optimización secuencial del circuito).

- Hachtel, Gary D .; Somenzi, Fabio (2006) [1996]. Algoritmos de Verificación y Síntesis Lógica . Springer Science & Business Media . ISBN 978-0-387-31005-3.

- Kohavi, Zvi; Jha, Niraj K. (2009). "4-6". Teoría de la conmutación y autómatas finitos (3ª ed.). Prensa de la Universidad de Cambridge . ISBN 978-0-521-85748-2.

- Knuth, Donald Ervin (2010). "7.1.2: Evaluación booleana". El arte de la programación informática . 4A . Addison-Wesley . págs. 96-133. ISBN 978-0-201-03804-0.

- Rutenbar, Rob A. Minimización de niveles múltiples, Parte I: Modelos y métodos (PDF) (diapositivas de la conferencia). Universidad Carnegie Mellon (CMU). Conferencia 7. Archivado (PDF) desde el original el 2018-01-15 . Consultado el 15 de enero de 2018 ; Rutenbar, Rob A. Minimización multinivel, Parte II: Extracto de cubo / coquenel (PDF) (diapositivas de la conferencia). Universidad Carnegie Mellon (CMU). Lección 8. Archivado (PDF) desde el original el 2018-01-15 . Consultado el 15 de enero de 2018 .

- Tomaszewski, Sebastian P .; Celik, Ilgaz U .; Antoniou, George E. (diciembre de 2003) [2005-03-05, 2002-04-09]. "Minimización de la función booleana basada en WWW" (PDF) . Revista Internacional de Matemática Aplicada e Informática . 13 (4): 577–584. Archivado (PDF) desde el original el 10 de mayo de 2020 . Consultado el 10 de mayo de 2020 . [50] [51] (7 páginas)

- Wilhelmy, Alexander; Kudielka, Viktor; Deussen, Peter; Böhling, Karl Heinz ; Händler, Wolfgang ; Neander, Joachim (enero de 1963) [18 de octubre de 1961]. Dörr, Johannes; Peschl, Ernst Ferdinand ; Unger, Heinz (eds.). 2. Coloquio sobre Schaltkreis- und Schaltwerk-Theorie - Vortragsauszüge vom 18. bis 20. Oktober 1961 en Saarbrücken . Internationale Schriftenreihe zur Numerischen Mathematik [Serie internacional de matemáticas numéricas] (ISNM) (en alemán). 4 (reimpresión del 20/12/2013 de la 1ª ed.). Institut für Angewandte Mathematik, Universität Saarbrücken , Rheinisch-Westfälisches Institut für Instrumentelle Mathematik: Springer Basel AG /Birkhäuser Verlag Basel . doi : 10.1007 / 978-3-0348-4156-6 . ISBN 978-3-0348-4081-1. Consultado el 15 de abril de 2020 . (152 páginas)

- Brayton, Robert King ; Rudell, Richard L .; Sangiovanni-Vincentelli, Alberto Luigi ; Wang, Albert R. (diciembre de 1987). "MIS: un sistema de optimización lógica de múltiples niveles" . Transacciones IEEE sobre diseño asistido por computadora de circuitos y sistemas integrados . 6 (6): 1062–1081. doi : 10.1109 / TCAD.1987.1270347 . (MIS) (20 páginas)