Anillo de protección

Este artículo incluye una lista de referencias generales , pero permanece en gran parte sin verificar porque carece de suficientes citas en línea correspondientes . ( Febrero de 2015 ) |

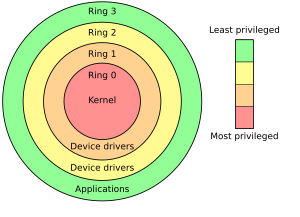

En informática , los dominios de protección jerárquica , [1] [2] a menudo llamados anillos de protección , son mecanismos para proteger los datos y la funcionalidad de fallas (mejorando la tolerancia a fallas ) y comportamiento malicioso (brindando seguridad informática ).

Los sistemas operativos informáticos proporcionan diferentes niveles de acceso a los recursos. Un anillo de protección es uno de dos o más niveles jerárquicos o capas de privilegios dentro de la arquitectura de un sistema informático . Esto es generalmente forzada por hardware por parte de algunos CPU arquitecturas que proporcionan diferentes modos de CPU en el hardware o el microcódigo de nivel. Los anillos se organizan en una jerarquía desde los más privilegiados (los más confiables, generalmente numerados con cero) hasta los menos privilegiados (los menos confiables, generalmente con el número de timbre más alto). En la mayoría de los sistemas operativos, Ring 0 es el nivel con más privilegios e interactúa más directamente con el hardware físico, como la CPU y la memoria.

Se proporcionan puertas de llamada especiales entre anillos para permitir que un anillo exterior acceda a los recursos de un anillo interior de una manera predefinida, en lugar de permitir un uso arbitrario. La puerta de acceso correcta entre anillos puede mejorar la seguridad al evitar que los programas de un anillo o nivel de privilegios hagan un mal uso de los recursos destinados a programas en otro. Por ejemplo, se debe evitar que el software espía que se ejecuta como un programa de usuario en Ring 3 encienda una cámara web sin informar al usuario, ya que el acceso al hardware debe ser una función de Ring 1 reservada para los controladores de dispositivos . Los programas como los navegadores web que se ejecutan en anillos con números más altos deben solicitar acceso a la red, un recurso restringido a un anillo con números más bajos.

Implementaciones

Los múltiples anillos de protección se encontraban entre los conceptos más revolucionarios introducidos por el sistema operativo Multics , un predecesor altamente seguro de la familia actual de sistemas operativos Unix. La computadora central GE 645 tenía cierto control de acceso de hardware, pero eso no era suficiente para brindar soporte completo para anillos en hardware, por lo que Multics los respaldaba mediante la captura de transiciones de anillo en software; [3] su sucesor, el Honeywell 6180 , los implementó en hardware, con soporte para ocho anillos. [4] Sin embargo, la mayoría de los sistemas de uso general usan solo dos anillos, incluso si el hardware en el que se ejecutan proporciona más modos de CPU.que eso. Por ejemplo, Windows 7 y Windows Server 2008 (y sus predecesores) usan solo dos anillos, con el anillo 0 correspondiente al modo kernel y el anillo 3 al modo de usuario , [5] porque las versiones anteriores de Windows se ejecutaban en procesadores que admitían solo dos niveles de protección. . [6]

Muchas arquitecturas de CPU modernas (incluida la popular arquitectura Intel x86 ) incluyen alguna forma de protección de anillo, aunque el sistema operativo Windows NT , como Unix, no utiliza completamente esta característica. OS / 2 lo hace hasta cierto punto, utilizando tres anillos: [7] anillo 0 para el código del kernel y controladores de dispositivo, anillo 2 para código privilegiado (programas de usuario con permisos de acceso de E / S) y anillo 3 para código no privilegiado (casi todos los usuarios programas). En DOS , el kernel, los controladores y las aplicaciones se ejecutan normalmente en el anillo 3 (sin embargo, esto es exclusivo del caso en el que se utilizan controladores en modo protegido y / o extensores de DOS; como un sistema operativo en modo real, el sistema se ejecuta efectivamente sin protección ), mientras que 386 administradores de memoria comoEMM386 se ejecuta en el anillo 0. Además de esto, EMM386 3.xx de DR-DOS puede ejecutar opcionalmente algunos módulos (como DPMS ) en el anillo 1. OpenVMS utiliza cuatro modos llamados (en orden de privilegios decrecientes) Kernel, Ejecutivo, Supervisor y Usuario.

Un interés renovado en esta estructura de diseño vino con la proliferación del software Xen VMM , la discusión en curso sobre monolíticos versus micro-kernels (particularmente en grupos de noticias Usenet y foros web ), la estructura de diseño Ring-1 de Microsoft como parte de su iniciativa NGSCB , y hipervisores basados en virtualización x86 como Intel VT-x (antes Vanderpool).

El sistema Multics original tenía ocho anillos, pero muchos sistemas modernos tienen menos. El hardware permanece consciente del anillo actual del subproceso de instrucción en ejecución en todo momento, con la ayuda de un registro de máquina especial. En algunos sistemas, a las áreas de la memoria virtual se les asignan números de timbre en el hardware. Un ejemplo es el Data General Eclipse MV / 8000 , en el que los tres bits superiores del contador de programa (PC) sirvieron como registro de anillo. Por lo tanto, el código que se ejecuta con la PC virtual configurada en 0xE200000, por ejemplo, estaría automáticamente en el anillo 7, y la llamada a una subrutina en una sección diferente de la memoria provocaría automáticamente una transferencia de anillo.

El hardware restringe severamente las formas en que se puede pasar el control de un anillo a otro y también impone restricciones sobre los tipos de acceso a la memoria que se pueden realizar entre los anillos. Usando x86 como ejemplo, hay una estructura de puerta especial [ aclaración necesaria ] a la que hace referencia la instrucción de llamada que transfiere el control de forma segura [ aclaración necesaria ] hacia puntos de entrada predefinidos en anillos de nivel inferior (más fiables); esto funciona como una llamada de supervisoren muchos sistemas operativos que utilizan la arquitectura de anillo. Las restricciones de hardware están diseñadas para limitar las oportunidades de infracciones de seguridad accidentales o malintencionadas. Además, el anillo más privilegiado puede recibir capacidades especiales (como direccionamiento de memoria real que omite el hardware de memoria virtual).

La arquitectura ARM versión 7 implementa tres niveles de privilegios: aplicación (PL0), sistema operativo (PL1) e hipervisor (PL2). Inusualmente, el nivel 0 (PL0) es el nivel con menos privilegios, mientras que el nivel 2 es el nivel con más privilegios. [8] ARM versión 8 implementa cuatro niveles de excepción: aplicación (EL0), sistema operativo (EL1), hipervisor (EL2) y monitor / firmware seguro (EL3), para AArch64 [9] : D1-2454 y AArch32. [9] : G1-6013

La protección de anillo se puede combinar con modos de procesador (maestro / núcleo / privilegiado / modo supervisor versus esclavo / no privilegiado / modo de usuario) en algunos sistemas. Los sistemas operativos que se ejecutan en hardware compatible con ambos pueden usar ambas formas de protección o solo una.

El uso eficaz de la arquitectura en anillo requiere una estrecha cooperación entre el hardware y el sistema operativo [ ¿por qué? ] . Los sistemas operativos diseñados para funcionar en múltiples plataformas de hardware pueden hacer un uso limitado de los anillos si no están presentes en todas las plataformas compatibles. A menudo, el modelo de seguridad se simplifica a "kernel" y "usuario", incluso si el hardware proporciona una granularidad más fina a través de anillos.

Modos

Modo supervisor

En términos informáticos, el modo supervisor es una bandera mediada por hardware que se puede cambiar mediante el código que se ejecuta en el software a nivel del sistema. Las tareas o subprocesos a nivel del sistema tendrán este indicador establecido mientras se ejecutan, mientras que las aplicaciones del espacio de usuario no. Esta bandera determina si sería posible ejecutar operaciones de código de máquina, como modificar registros para varias tablas de descriptores, o realizar operaciones como desactivar interrupciones. La idea de tener dos modos diferentes para operar proviene de "con más control viene más responsabilidad": se confía en que un programa en modo supervisor nunca fallará, ya que una falla puede hacer que todo el sistema informático se bloquee.

El modo supervisor es "un modo de ejecución en algunos procesadores que permite la ejecución de todas las instrucciones, incluidas las instrucciones privilegiadas. También puede dar acceso a un espacio de direcciones diferente, al hardware de administración de memoria y a otros periféricos. Este es el modo en el que el sistema operativo normalmente se ejecuta ". [10]

En un kernel monolítico , el sistema operativo se ejecuta en modo supervisor y las aplicaciones se ejecutan en modo usuario. Otros tipos de sistemas operativos , como los que tienen un exokernel o microkernel , no necesariamente comparten este comportamiento.

Algunos ejemplos del mundo de la PC:

- Linux , macOS y Windows son tres sistemas operativos que utilizan el modo supervisor / usuario. Para realizar funciones especializadas, el código de modo de usuario debe realizar una llamada al sistema en modo supervisor o incluso al espacio del kernel donde el código de confianza del sistema operativo realizará la tarea necesaria y devolverá la ejecución al espacio de usuario. Se puede agregar código adicional al espacio del kernel mediante el uso de módulos del kernel cargables , pero solo por un usuario con los permisos necesarios, ya que este código no está sujeto al control de acceso y las limitaciones de seguridad del modo de usuario.

- DOS (mientras no se cargue un administrador de memoria 386 como EMM386 ), así como otros sistemas operativos simples y muchos dispositivos integrados se ejecutan en modo supervisor de forma permanente, lo que significa que los controladores se pueden escribir directamente como programas de usuario.

La mayoría de los procesadores tienen al menos dos modos diferentes. Los procesadores x86 tienen cuatro modos diferentes divididos en cuatro anillos diferentes. Los programas que se ejecutan en Ring 0 pueden hacer cualquier cosa con el sistema, y el código que se ejecuta en Ring 3 debería poder fallar en cualquier momento sin afectar al resto del sistema informático. El anillo 1 y el anillo 2 rara vez se utilizan, pero se pueden configurar con diferentes niveles de acceso.

En la mayoría de los sistemas existentes, cambiar del modo de usuario al modo de kernel tiene un alto costo asociado en el rendimiento. Se ha medido, en la solicitud básica getpid, que cuesta entre 1000 y 1500 ciclos en la mayoría de las máquinas. De estos, alrededor de 100 son para el cambio real (70 del usuario al espacio del kernel y 40 hacia atrás), el resto es "sobrecarga del kernel". [11] [12] En el micronúcleo L3 , la minimización de estos gastos generales redujo el costo total a alrededor de 150 ciclos. [11]

Maurice Wilkes escribió: [13]

... finalmente quedó claro que la protección jerárquica que proporcionaban los anillos no coincidía con los requisitos del programador del sistema y proporcionaba poca o ninguna mejora en el sistema simple de tener solo dos modos. Los anillos de protección se prestaban a una implementación eficiente en hardware, pero había poco más que decir sobre ellos. [...] El atractivo de la protección de grano fino se mantuvo, incluso después de que se vio que los anillos de protección no proporcionaban la respuesta ... Esto nuevamente resultó ser un callejón sin salida ...

Para obtener rendimiento y determinismo, algunos sistemas colocan funciones que probablemente se verían como lógica de aplicación, en lugar de controladores de dispositivo, en modo kernel; Las aplicaciones de seguridad ( control de acceso , cortafuegos , etc.) y los monitores del sistema operativo se citan como ejemplos. Al menos un sistema de administración de base de datos integrado, e X treme DB Kernel Mode , se ha desarrollado específicamente para la implementación del modo kernel, para proporcionar una base de datos local para las funciones de aplicaciones basadas en el kernel y para eliminar los cambios de contexto que de otro modo ocurrirían cuando las funciones del kernel interactúan. con un sistema de base de datos que se ejecuta en modo de usuario. [14]

Las funciones también se mueven a veces a través de anillos en la otra dirección. El kernel de Linux, por ejemplo, inyecta una sección vDSO en los procesos que contiene funciones que normalmente requerirían una llamada al sistema, es decir, una transición de anillo. Pero en lugar de realizar una llamada al sistema, estas funciones utilizan datos estáticos proporcionados por el kernel, lo que evita la necesidad de una transición de anillo que es más ligera que una llamada al sistema. La función gettimeofday se puede proporcionar de esta manera.

Modo de hipervisor

Las CPU recientes de Intel y AMD ofrecen instrucciones de virtualización x86 para que un hipervisor controle el acceso al hardware Ring 0. Aunque son mutuamente incompatibles, tanto Intel VT-x (con nombre en código "Vanderpool") como AMD-V (con nombre en código "Pacifica") crean un nuevo "Ring -1" para que un sistema operativo invitado pueda ejecutar operaciones de Ring 0 de forma nativa sin afectar a otros invitados o el sistema operativo anfitrión.

Para ayudar a la virtualización, VT-x y SVM insertan un nuevo nivel de privilegio debajo del anillo 0. Ambos agregan nueve nuevas instrucciones de código de máquina que solo funcionan en "Ring −1", destinadas a ser utilizadas por el hipervisor. [15]

Nivel de privilegio

Un nivel de privilegio en el conjunto de instrucciones x86 controla el acceso del programa que se ejecuta actualmente en el procesador a recursos como regiones de memoria, puertos de E / S e instrucciones especiales. Hay 4 niveles de privilegios que van desde 0, que es el más privilegiado, hasta 3, que es el menos privilegiado. La mayoría de los sistemas operativos modernos usan el nivel 0 para el núcleo / ejecutivo y el nivel 3 para los programas de aplicación. Cualquier recurso disponible para el nivel n también está disponible para los niveles 0 an, por lo que los niveles de privilegio son anillos. Cuando un proceso con menos privilegios intenta acceder a un proceso con más privilegios, se informa al sistema operativo una excepción de falla de protección general .

No es necesario utilizar los cuatro niveles de privilegios. Los sistemas operativos actuales con una amplia participación de mercado, incluidos Microsoft Windows , macOS , Linux , iOS y Android, utilizan principalmente un mecanismo de paginación con solo un bit para especificar el nivel de privilegio como Supervisor o Usuario (U / S Bit). Windows NT utiliza el sistema de dos niveles. [16] Los programas en modo real en 8086 se ejecutan en el nivel 0 (nivel de privilegio más alto) mientras que el modo virtual en 8086 ejecuta todos los programas en el nivel 3. [17]

Los posibles usos futuros de los múltiples niveles de privilegios admitidos por la familia ISA x86 incluyen la contenedorización y las máquinas virtuales . Un kernel de sistema operativo host podría usar instrucciones con acceso con privilegios completos ( modo kernel ), mientras que las aplicaciones que se ejecutan en el sistema operativo invitado en una máquina virtual o contenedor podrían usar el nivel más bajo de privilegios en modo de usuario. La máquina virtual y el kernel del sistema operativo invitado podrían utilizar un nivel intermedio de privilegios de instrucción para invocar y virtualizar operaciones en modo kernel, como las llamadas al sistema, desde el punto de vista del sistema operativo invitado. [18]

IOPL

El indicador IOPL ( nivel de privilegio de E / S ) es un indicador que se encuentra en todas las CPU x86 compatibles con IA-32 . Ocupa los bits 12 y 13 del registro FLAGS . En modo protegido y modo largo , muestra el nivel de privilegio de E / S del programa o tarea actual. El privilegio Nivel actual (CPL) (CPL0, CPL 1, CPL2, CPL3) de la tarea o programa debe ser menor o igual a la IOPL para que la tarea o programa para el acceso de E / S de los puertos .

El IOPL se puede cambiar usando POPF(D)y IRET(D)solo cuando el nivel de privilegio actual es Ring 0.

Además de IOPL, los permisos del puerto de E / S en el TSS también participan en la determinación de la capacidad de una tarea para acceder a un puerto de E / S.

Misc

En los sistemas x86, la virtualización de hardware x86 ( VT-x y SVM ) se denomina "anillo -1", el modo de gestión del sistema se denomina "anillo -2", el motor de gestión Intel y el procesador de seguridad de la plataforma AMD a veces se denominan "anillo -3". [19]

Uso de funciones de hardware

Muchas arquitecturas de hardware de CPU proporcionan mucha más flexibilidad de la que aprovechan los sistemas operativos que normalmente ejecutan. El uso adecuado de los modos de CPU complejos requiere una cooperación muy estrecha entre el sistema operativo y la CPU y, por lo tanto, tiende a vincular el sistema operativo a la arquitectura de la CPU. Cuando el sistema operativo y la CPU están diseñados específicamente el uno para el otro, esto no es un problema (aunque algunas características de hardware pueden quedar sin explotar), pero cuando el sistema operativo está diseñado para ser compatible con múltiples arquitecturas de CPU diferentes, una gran parte de el SO puede ignorar las funciones del modo CPU. Por ejemplo, la razón por la que Windows usa solo dos niveles (anillo 0 y anillo 3) es que algunas arquitecturas de hardware que eran compatibles en el pasado (como PowerPC o MIPS) implementó solo dos niveles de privilegios. [5]

Multics era un sistema operativo diseñado específicamente para una arquitectura de CPU especial (que a su vez fue diseñado específicamente para Multics), y aprovechó al máximo los modos de CPU disponibles. Sin embargo, fue una excepción a la regla. Hoy en día, este alto grado de interoperación entre el sistema operativo y el hardware no suele ser rentable, a pesar de las posibles ventajas para la seguridad y la estabilidad.

En última instancia, el propósito de los distintos modos de funcionamiento de la CPU es proporcionar protección de hardware contra la corrupción accidental o deliberada del entorno del sistema (y las correspondientes brechas de seguridad del sistema) por parte del software. Solo las partes "confiables" del software del sistema pueden ejecutarse en el entorno sin restricciones del modo kernel, y luego, en diseños paradigmáticos, solo cuando sea absolutamente necesario. El resto del software se ejecuta en uno o más modos de usuario. Si un procesador genera una condición de falla o excepción en un modo de usuario, en la mayoría de los casos la estabilidad del sistema no se ve afectada; Si un procesador genera una condición de falla o excepción en el modo kernel, la mayoría de los sistemas operativos detendrán el sistema con un error irrecuperable. Cuando existe una jerarquía de modos (seguridad basada en anillos),las fallas y excepciones en un nivel de privilegios pueden desestabilizar solo los niveles de privilegios con números más altos. Por lo tanto, una falla en Ring 0 (el modo de kernel con el mayor privilegio) colapsará todo el sistema, pero una falla en Ring 2 solo afectará a Rings 3 y posteriores y al Ring 2 en sí, como máximo.

Las transiciones entre modos quedan a discreción del subproceso de ejecución cuando la transición es de un nivel de privilegio alto a uno de privilegio bajo (como de kernel a modos de usuario), pero las transiciones de niveles de privilegio más bajos a más altos solo pueden tener lugar a través de un sistema seguro. , "puertas" controladas por hardware que se atraviesan mediante la ejecución de instrucciones especiales o cuando se reciben interrupciones externas.

Los sistemas operativos de microkernel intentan minimizar la cantidad de código que se ejecuta en modo privilegiado, por motivos de seguridad y elegancia , pero en última instancia, sacrifican el rendimiento.

Ver también

- Puerta de llamada (Intel)

- Segmentación de la memoria

- Modo protegido : disponible en CPU 80286 compatibles con x86 y posteriores

- IOPL (directiva CONFIG.SYS) : una directiva OS / 2 para ejecutar código DLL en el anillo 2 en lugar de en el anillo 3

- Descriptor de segmento

- Instrucción de llamada de supervisor

- Modo de gestión del sistema (SMM)

- Principio de privilegio mínimo

Referencias

- ^ Karger, Paul A .; Herbert, Andrew J. (1984). "Una arquitectura de capacidad aumentada para respaldar la seguridad de celosía y la trazabilidad del acceso". 1984 Simposio IEEE sobre seguridad y privacidad . pag. 2. doi : 10.1109 / SP.1984.10001 . ISBN 0-8186-0532-4. S2CID 14788823 .

- ^ Carpeta, W. (2001). "Diseño e implementación del kernel de agente móvil J-SEAL2". Actas 2001 Simposio sobre aplicaciones e Internet . págs. 35–42. doi : 10.1109 / SAINT.2001.905166 . ISBN 0-7695-0942-8. S2CID 11066378 .

- ^ "Una arquitectura de hardware para implementar anillos de protección" . Consultado el 27 de septiembre de 2012 .

- ^ "Glosario de Multics - anillo" . Consultado el 27 de septiembre de 2012 .

- ↑ a b Russinovich, Mark E .; David A. Solomon (2005). Internos de Microsoft Windows (4 ed.). Microsoft Press. pp. 16 . ISBN 978-0-7356-1917-3.

- ^ Russinovich, Mark (2012). Partes internas de Windows, parte 1. 6th Ed . Redmond, Washington: Microsoft Press. pag. 17. ISBN 978-0-7356-4873-9.

La razón por la que Windows usa solo dos niveles es que algunas arquitecturas de hardware que fueron compatibles en el pasado (como Compaq Alpha y Silicon Graphics MIPS ) implementaron solo dos niveles de privilegios.

- ^ "Referencia del controlador de dispositivo de presentación para OS / 2 - 5. Introducción a los controladores de presentación de OS / 2" . Archivado desde el original el 15 de junio de 2015 . Consultado el 13 de junio de 2015 .

- ^ ARM Architecture Reference Manual ARMv7-A y edición ARMv7-R . Arm Ltd. pág. B1-1136.

- ^ Un b Brazo Arquitectura Manual de referencia ARMv8, para la arquitectura A-perfil . Arm Ltd.

- ^ "modo supervisor" . FOLDOC . 15 de febrero de 1995.

- ^ a b Jochen Liedtke . Sobre la construcción de µ-Kernel , Proc. 15 ° Simposio de ACM sobre principios de sistemas operativos (SOSP) , diciembre de 1995

- ^ Ousterhout, JK 1990. ¿Por qué los sistemas operativos no son tan rápidos como el hardware? En Usenix Summer Conference, Anaheim, CA, págs. 247-256.

- ^ Maurice Wilkes (abril de 1994). "Sistemas operativos en un mundo cambiante". Revisión de sistemas operativos ACM SIGOPS . 28 (2): 9-21. doi : 10.1145 / 198153.198154 . ISSN 0163-5980 . S2CID 254134 .

- ^ Gorine, Andrei y Krivolapov, Alexander. "Bases de datos en modo kernel: una tecnología DBMS para aplicaciones de alto rendimiento" , Dr. Dobb's Journal , mayo de 2008.

- ^ Dornan, Andy (1 de noviembre de 2005). "Intel VT contra AMD Pacifica" . CMP. Archivado desde el original el 30 de mayo de 2013 . Consultado el 11 de noviembre de 2012 .

- ^ Russinovich, Mark E .; David A. Solomon (2005). Internos de Microsoft Windows (4 ed.). Microsoft Press. págs. 16. ISBN 978-0-7356-1917-3

- ^ Sunil Mathur, "Microprocesador 8086: Arquitectura, programación e interfaz", Edición de economía oriental, PHI Learning

- ^ Anderson, Thomas; Dahlin, Michael (21 de agosto de 2014). "2,2". Sistemas operativos: principios y práctica (2ª ed.). Libros recursivos. ISBN 978-0985673529.

- ^ Gelas, Johan De. "Virtualización de hardware: tuercas y tornillos" . www.anandtech.com . Consultado el 13 de marzo de 2021 .

- Referencia del programador Intel 80386

Otras lecturas

- David T. Rogers (junio de 2003). "Un marco para la subversión dinámica" (PDF) .

- William J. Caelli (2002). "Volver a aprender" sistemas de confianza "en una era de PIIN: lecciones del pasado para el futuro" (PDF) .

- Haruna R. Isa; William R. Shockley; Cynthia E. Irvine (1999). "Una arquitectura de subprocesos múltiples para el procesamiento de transacciones seguras multinivel" (PDF) .

- Ivan Kelly (8 de mayo de 2006). "Portando MINIX a Xen" (PDF) . Archivado desde el original (PDF) el 27 de agosto de 2006.

- Paul Barham; Boris Dragovic; Keir Fraser; Steven Hand; Tim Harris; Alex Ho; Rolf Neugebauer; Ian Pratt; Andrew Warfield (2003). "Xen y el arte de la virtualización" (PDF) .

- Marcus Peinado; Yuqun Chen; Paul England; John Manferdelli. "NGSCB: un sistema abierto de confianza" (PDF) . Archivado desde el original (PDF) el 4 de marzo de 2005.

- Michael D. Schroeder ; Jerome H. Saltzer (1972). "Una arquitectura de hardware para implementar anillos de protección" .

- "Manual del desarrollador de software de la arquitectura Intel Volumen 3: Programación del sistema (número de pedido 243192)" (PDF) . Capítulo 4 "Protección"; sección 4.5 "Niveles de privilegio". Archivado desde el original (PDF) el 19 de febrero de 2009.

- Tzi-cker Chiueh; Ganesh Venkitachalam; Prashant Pradhan (1999). "Integrando segmentación y protección de paginación para extensiones de software seguras, eficientes y transparentes" . Capítulo 3: Funciones de hardware de protección en la arquitectura Intel X86; sección 3.1 Comprobaciones de protección.

- Takahiro Shinagawa; Kenji Kono; Takashi Masuda (17 de mayo de 2000). "Explotación del mecanismo de segmentación para la protección contra código móvil malicioso" (PDF) . Capítulo 3 Implementación; sección 3.2.1 Protección del anillo. Archivado desde el original (PDF) el 10 de agosto de 2017 . Consultado el 2 de abril de 2018 .

- Boebert, William Earl; R. Kain (1985). Una alternativa práctica a las políticas de integridad jerárquica . VIII Congreso Nacional de Seguridad Informática.

- Gorine, Andrei; Krivolapov, Alexander (mayo de 2008). "Bases de datos en modo kernel: una tecnología DBMS para aplicaciones de alto rendimiento" . Diario del Dr. Dobb .

- Unidad Central de procesamiento

- Modelos de seguridad informática

- Tecnología del sistema operativo