Intel 8259

Este artículo incluye una lista de referencias generales , pero permanece en gran parte sin verificar porque carece de suficientes citas en línea correspondientes . ( Septiembre de 2013 ) |

El Intel 8259 es un controlador de interrupción programable (PIC) diseñado para los Intel 8085 y Intel 8086 microprocesadores . La parte inicial era 8259, una versión posterior con sufijo A era compatible con versiones superiores y se podía usar con el procesador 8086 o 8088 . El 8259 combina múltiples fuentes de entrada de interrupción en una sola salida de interrupción al microprocesador host, extendiendo los niveles de interrupción disponibles en un sistema más allá de uno o dos niveles que se encuentran en el chip del procesador. El 8259A era el controlador de interrupciones para el bus ISA en el IBM PC original y el IBM PC AT .

El 8259 se introdujo como parte de la familia MCS 85 de Intel en 1976. El 8259A se incluyó en el PC original presentado en 1981 y fue mantenido por el PC / XT cuando se presentó en 1983. Se agregó un segundo 8259A con la introducción del PC / AT . El 8259 ha coexistido con la arquitectura Intel APIC desde su introducción en las PC multiprocesador simétrico . Las PC modernas han comenzado a eliminar gradualmente el 8259A a favor de la arquitectura Intel APIC . Sin embargo, aunque ya no es un chip separado, la interfaz 8259A sigue siendo proporcionada por el Platform Controller Hub o el chipset Southbridge en las placas base x86 modernas .[1]

Descripcion funcional

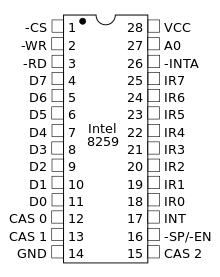

Los pines de señal principal en un 8259 son los siguientes: ocho líneas de solicitud de entrada de interrupción llamadas IRQ0 a IRQ7, una línea de salida de solicitud de interrupción llamada INTR, línea de reconocimiento de interrupción llamada INTA, D0 a D7 para comunicar el nivel de interrupción o el desplazamiento vectorial. Otras conexiones incluyen CAS0 a CAS2 para conexión en cascada entre 8259s.

Se pueden conectar en cascada hasta ocho 8259 esclavos a un 8259 maestro para proporcionar hasta 64 IRQ. Los 8259 se conectan en cascada conectando la línea INT de un 8259 esclavo a la línea IRQ de un 8259 maestro .

Hay tres registros, un registro de máscara de interrupción (IMR), un registro de solicitud de interrupción (IRR) y un registro en servicio (ISR). El IRR mantiene una máscara de las interrupciones actuales que están pendientes de reconocimiento, el ISR mantiene una máscara de las interrupciones que están pendientes de una EOI y el IMR mantiene una máscara de interrupciones que no deben enviarse como reconocimiento.

Las operaciones de fin de interrupción (EOI) admiten EOI específicas, EOI no específicas y EOI automáticas. Una EOI específica especifica el nivel de IRQ que reconoce en el ISR. Una EOI no específica restablece el nivel de IRQ en el ISR. Auto-EOI restablece el nivel de IRQ en el ISR inmediatamente después de que se reconoce la interrupción.

Los modos de disparo de interrupción por flanco y nivel son compatibles con el 8259A. Se admiten los modos de prioridad fija y de prioridad rotativa.

El 8259 puede configurarse para funcionar con un 8080/8085 o un 8086/8088. En el 8086/8088, el controlador de interrupciones proporcionará un número de interrupción en el bus de datos cuando ocurra una interrupción. El ciclo de interrupción del 8080/8085 emitirá tres bytes en el bus de datos (correspondiente a una instrucción CALL en el conjunto de instrucciones 8080/8085).

El 8259A proporciona una funcionalidad adicional en comparación con el 8259 (en particular, el modo con búfer y el modo activado por nivel) y es compatible con versiones posteriores.

Consideraciones de programación

DOS y Windows

La programación de un 8259 junto con DOS y Microsoft Windows ha introducido una serie de problemas confusos en aras de la compatibilidad con versiones anteriores, que se remontan a la PC original presentada en 1981.

El primer problema es más o menos la raíz del segundo problema. Se espera que los controladores de dispositivos DOS envíen una EOI no específica a los 8259 cuando terminen de reparar su dispositivo. Esto evita el uso de cualquiera de los otros modos EOI del 8259 en DOS y excluye la diferenciación entre las interrupciones del dispositivo redirigidas desde el 8259 maestro al 8259 esclavo.

El segundo tema trata sobre el uso de IRQ2 e IRQ9 a partir de la introducción de un esclavo 8259 en el PC / AT. La salida INT del esclavo 8259 está conectada al IR2 del maestro. La línea IRQ2 del bus ISA, originalmente conectada a este IR2, se redireccionó al IR1 del esclavo. Por lo tanto, la antigua línea IRQ2 ahora genera IRQ9 en la CPU. Para permitir la compatibilidad con versiones anteriores de los controladores de dispositivo DOS que aún están configurados para IRQ2, el BIOS instala un controlador para IRQ9 que redirige las interrupciones al controlador IRQ2 original.

En la PC, el BIOS (y por lo tanto también DOS) mapea tradicionalmente las solicitudes de interrupción 8259 maestras (IRQ0-IRQ7) para interrumpir el vector de compensación 8 (INT08-INT0F) y las solicitudes de interrupción 8259 esclavas (en PC / AT y posteriores) (IRQ8) -IRQ15) para interrumpir el desplazamiento vectorial 112 (INT70-INT77). Esto se hizo a pesar de que el procesador reservaba los primeros 32 vectores de interrupción (INT00-INT1F) para excepciones internas (esto se ignoró para el diseño de la PC por alguna razón). Debido a los vectores reservados para excepciones, la mayoría de los otros sistemas operativos mapean (al menos el maestro) 8259 IRQ (si se usan en una plataforma) a otro desplazamiento de base de vector de interrupción.

Otros sistemas operativos

Dado que la mayoría de los demás sistemas operativos permiten cambios en las expectativas del controlador del dispositivo, se pueden usar otros modos de operación 8259, como Auto-EOI. Esto es especialmente importante para el hardware x86 moderno en el que se puede dedicar una cantidad significativa de tiempo a la demora del espacio de direcciones de E / S al comunicarse con los 8259. Esto también permite una serie de otras optimizaciones en sincronización, como secciones críticas, en un sistema x86 multiprocesador con 8259s.

Modos activados por borde y nivel

Dado que el bus ISA no admite interrupciones activadas por nivel , el modo activado por nivel no se puede utilizar para interrupciones conectadas a dispositivos ISA. Esto significa que en PC / XT, PC / AT y sistemas compatibles, el 8259 debe programarse para el modo de activación por flanco . En los sistemas MCA, los dispositivos utilizan interrupciones activadas por nivel y el controlador de interrupciones está cableado para funcionar siempre en modo activado por nivel. En los sistemas EISA, PCI y posteriores más nuevos, los registros de control de borde / nivel (ELCR) controlan el modo por línea IRQ, lo que hace que el modo del 8259 sea irrelevante para dichos sistemas con buses ISA. El BIOS programa el ELCR al iniciar el sistema para que funcione correctamente.

Los ELCR se encuentran 0x4d0 y 0x4d1 en el espacio de direcciones de E / S x86. Tienen un ancho de 8 bits y cada bit corresponde a una IRQ de los 8259. Cuando se establece un bit, la IRQ está en modo activado por nivel; de lo contrario, la IRQ está en modo de activación por flanco.

Interrupciones espurias

El 8259 genera interrupciones falsas en respuesta a una serie de condiciones.

La primera es una línea IRQ que se anula antes de que se reconozca. Esto puede ocurrir debido al ruido en las líneas IRQ. En el modo de activación por flanco, el ruido debe mantener la línea en el estado bajo durante 100 ns. Cuando el ruido disminuye, una resistencia pull-up devuelve la línea IRQ a alta, generando así una falsa interrupción. En el modo activado por nivel, el ruido puede causar un nivel alto de señal en la línea INTR del sistema. Si el sistema envía una solicitud de confirmación, el 8259 no tiene nada que resolver y, por lo tanto, envía un IRQ7 en respuesta. Este primer caso generará IRQ7 falsos.

Un caso similar puede ocurrir cuando el desenmascaramiento de 8259 y la desaserción de la entrada de IRQ no están sincronizados correctamente. En muchos sistemas, la entrada de IRQ se anula mediante una escritura de E / S y el procesador no espera hasta que la escritura llega al dispositivo de E / S. Si el procesador continúa y desenmascara el 8259 IRQ antes de que se anule la entrada de IRQ, el 8259 reafirmará INTR nuevamente. En el momento en que el procesador reconoce este INTR y emite un acuse de recibo para leer el IRQ del 8259, la entrada del IRQ se puede anular y el 8259 devuelve un IRQ7 falso.

El segundo es que el IRQ2 del maestro 8259 está activo alto cuando las líneas de IRQ del esclavo 8259 están inactivas en el flanco descendente de un reconocimiento de interrupción. Este segundo caso generará IRQ15 falsos, pero es raro.

PC / XT y PC / AT

El sistema PC / XT ISA tenía un controlador 8259, mientras que los sistemas PC / AT y posteriores tenían dos controladores 8259, maestro y esclavo. IRQ0 a IRQ7 son las líneas de interrupción del 8259 maestro, mientras que IRQ8 a IRQ15 son las líneas de interrupción del 8259 esclavo. Las etiquetas de los pines de un 8259 son de IR0 a IR7. IRQ0 a IRQ15 son los nombres de las líneas del bus ISA a las que están conectados los 8259.

Variantes

| Número de modelo | Tecnología | Rango de temperatura | Fecha de lanzamiento | Precio (USD) [lista 1] |

|---|---|---|---|---|

| ID8259 | -40 ° C a + 85 ° C [2] | Marzo / abril de 1979 [3] | $ 23.15 | |

| M8259 | Militar | Marzo / abril de 1979 [4] | $ 95.00 | |

| 82C59A [5] | CMOS | Julio / agosto de 1984 |

- ^ En cantidades de 100 y más

Ver también

- Controlador de interrupciones programable avanzado (APIC)

- IF (bandera x86)

- Controlador de interrupciones

- Interrupción de latencia

- Interrupción no enmascarable (NMI)

- Controlador de interrupción programable (PIC)

Referencias

- ^ http://pdf.datasheetcatalog.com/datasheet/Intel/mXvqwzr.pdf

- ^ Intel Corporation, "8086 disponible para entornos industriales", edición especial de Intel Preview: soluciones de 16 bits, mayo / junio de 1980, página 29

- ^ Intel Corporation, "Componente de microcomputadora: la nueva línea de productos de grado industrial responde a la demanda de componentes de alta confiabilidad para operar en aplicaciones industriales", Intel Preview, marzo / abril de 1979, pág. 11

- ^ Intel Corporation, "Productos militares: ¡Intel marcha!", Intel Preview, marzo / abril de 1979, pág. 19

- ^ Intel Corporation, "NewsBit: Intel Licenses Oki en la versión CMOS de varios productos", Soluciones, julio / agosto de 1984, página 1.

- Gilluwe, Frank van. La PC indocumentada . AW Developers Press, 1997. ISBN 0-201-47950-8

- McGivern, Joseph. Diseño de sistema de PC impulsado por interrupciones . Annabooks, 1998. ISBN 0-929392-50-7

- Referencia técnica de la interfaz de hardware de IBM Personal System / 2: arquitecturas . IBM, 1990. Publicación de IBM 84F8933

enlaces externos

- Controlador de interrupciones programable 8259A

- Conjuntos de chips Intel

- Compatible con IBM PC

- Circuitos integrados de entrada / salida

- Interrupciones