PowerPC 600

La familia PowerPC 600 fue la primera familia de procesadores PowerPC construida. Fueron diseñados en las instalaciones de Somerset en Austin, Texas , financiados conjuntamente y atendidos por ingenieros de IBM y Motorola como parte de la alianza AIM . Somerset se inauguró en 1992 y su objetivo era fabricar el primer procesador PowerPC y luego seguir diseñando procesadores PowerPC de uso general para computadoras personales . La primera encarnación se convirtió en el PowerPC 601 en 1993, y la segunda generación pronto siguió con el PowerPC 603, PowerPC 604 y el PowerPC 620 de 64 bits.

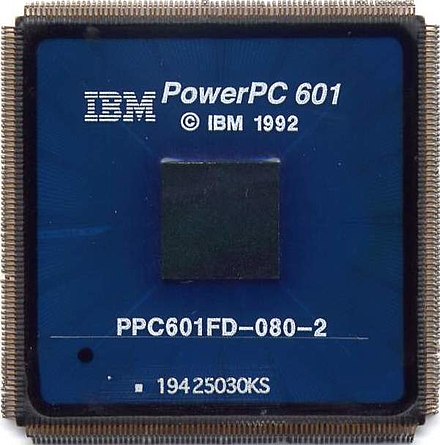

El PowerPC 601 fue la primera generación de microprocesadores que admitió el conjunto básico de instrucciones PowerPC de 32 bits . El esfuerzo de diseño comenzó en serio a mediados de 1991 y los primeros chips prototipo estuvieron disponibles en octubre de 1992. Los primeros procesadores 601 se introdujeron en una estación de trabajo IBM RS / 6000 en octubre de 1993 (junto con su primo multichip más potente de la línea de procesadores IBM POWER2 ) y los primeros Apple Power Macintosh el 14 de marzo de 1994. El 601 fue la primera implementación avanzada de un solo chip de la arquitectura POWER / PowerPC diseñada en un programa de choque para establecer PowerPC en el mercado y consolidar la alianza AIM. Para lograr un cronograma extremadamente agresivo y al mismo tiempo incluir una funcionalidad sustancialmente nueva (como mejoras sustanciales de rendimiento, nuevas instrucciones y, lo que es más importante, la primera implementación de multiprocesamiento simétrico (SMP) de POWER / PowerPC ), el diseño aprovechó una serie de tecnologías clave y estrategias de gestión de proyectos. El equipo 601 aprovechó gran parte de la estructura básica y partes del procesador IBM RISC Single Chip (RSC), [1] pero también incluyó soporte para la gran mayoría de las nuevas instrucciones PowerPC que no están en elConjunto de instrucciones POWER . Si bien casi todas las partes del diseño de RSC se modificaron y muchos bloques de diseño se modificaron sustancialmente o se rediseñaron por completo, dada la estructura de bus de E / S unificada completamente diferente y el soporte de coherencia de memoria / SMP . Los nuevos cambios de PowerPC, aprovechando la estructura básica de RSC, fue muy beneficioso para reducir la incertidumbre en el área de chips / planificación de piso y análisis / ajuste de tiempos. Vale la pena señalar que el 601 no solo implementó nuevas funciones clave sustanciales como SMP, sino que también actuó como un puente entre el POWER y los futuros procesadores PowerPC para ayudar a IBM y a los desarrolladores de software en su transición a PowerPC. Desde el inicio del diseño hasta el cierredel primer prototipo 601 fueron solo 12 meses para presionar duro para establecer PowerPC en el mercado temprano.

Para ayudar al esfuerzo de incorporar rápidamente la arquitectura del bus 88110 al 601 en beneficio de la alianza y sus clientes, la administración de Motorola proporcionó no solo las especificaciones de la arquitectura del bus 88110, sino también un puñado de diseñadores con conocimientos de bus 88110 para ayudar con la implementación y verificación de la lógica del bus 60x. Dado que el equipo de diseño del sistema de Apple estaba familiarizado con la estructura del bus de E / S del 88110 de Motorola y esta implementación del bus de E / S estaba bien definida y documentada, el equipo 601 adoptó la tecnología del bus para mejorar el tiempo de comercialización. El bus fue rebautizado como bus 60x una vez implementado en el 601. [2] Estos diseñadores de Motorola (y un pequeño número de Apple) se unieron a más de 120 diseñadores de IBM para crear el 601.

El uso del autobús 88110 como base para el autobús 60x ayudó a los horarios de varias maneras. Ayudó al equipo de Apple Power Macintosh al reducir la cantidad de rediseño de sus ASIC de soporte y redujo la cantidad de tiempo necesario para que los diseñadores y arquitectos de procesadores propongan, documenten, negocien y cierren una nueva interfaz de bus (evitando con éxito el "Bus Guerras "esperadas por el equipo de gestión del 601 si el autobús 88110 o los autobuses RSC anteriores no se habían adoptado). Vale la pena señalar que aceptar el bus 88110 en beneficio de los esfuerzos de Apple y la alianza fue a expensas de los esfuerzos del primer equipo de diseño del sistema IBM RS / 6000 que ya tenía sus ASIC de soporte implementados alrededor de la estructura de bus totalmente diferente de RSC.