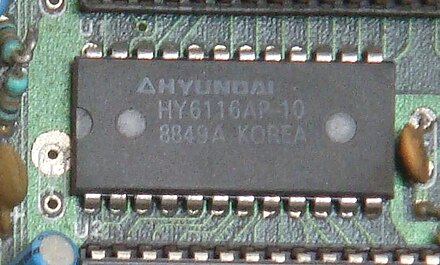

Memoria estática de acceso aleatorio

La memoria estática de acceso aleatorio ( RAM estática o SRAM ) es un tipo de memoria de acceso aleatorio (RAM) que utiliza un circuito de bloqueo (flip-flop) para almacenar cada bit. SRAM es memoria volátil ; los datos se pierden cuando se quita la energía.

El término 'estático' diferencia SRAM de DRAM ( memoria dinámica de acceso aleatorio) que debe actualizarse periódicamente . SRAM es más rápido y más caro que DRAM; por lo general, se usa para el caché y los registros internos de una CPU , mientras que la DRAM se usa para la memoria principal de una computadora .

La SRAM bipolar de semiconductores fue inventada en 1963 por Robert Norman en Fairchild Semiconductor. [1] MOS SRAM fue inventado en 1964 por John Schmidt en Fairchild Semiconductor. Era una SRAM de canal p MOS de 64 bits. [2] [3]

La SRAM fue el principal impulsor detrás de cualquier nuevo proceso de fabricación de tecnología basada en CMOS desde 1959, cuando se inventó el CMOS. [4] En 1965, [5] Arnold Farber y Eugene Schlig, que trabajaban para IBM, crearon una celda de memoria cableada usando una puerta de transistor y un diodo de túnel . Reemplazaron el pestillo con dos transistores y dos resistencias , una configuración que se conoció como la celda de Farber-Schlig. En 1965, Benjamin Agusta y su equipo de IBM crearon un chip de memoria de silicio de 16 bits basado en la celda Farber-Schlig, con 80 transistores, 64 resistencias y 4 diodos.

SRAM ofrece un modelo de acceso a datos simple y no requiere un circuito de actualización. El rendimiento y la confiabilidad son buenos y el consumo de energía es bajo cuando está inactivo. [7]

Dado que SRAM requiere más transistores por bit para implementarse, es menos denso y más costoso que DRAM y también tiene un mayor consumo de energía durante el acceso de lectura o escritura. El consumo de energía de SRAM varía ampliamente según la frecuencia con la que se accede a ella. [7]